ТОР 5 статей:

Методические подходы к анализу финансового состояния предприятия

Проблема периодизации русской литературы ХХ века. Краткая характеристика второй половины ХХ века

Характеристика шлифовальных кругов и ее маркировка

Служебные части речи. Предлог. Союз. Частицы

КАТЕГОРИИ:

- Археология

- Архитектура

- Астрономия

- Аудит

- Биология

- Ботаника

- Бухгалтерский учёт

- Войное дело

- Генетика

- География

- Геология

- Дизайн

- Искусство

- История

- Кино

- Кулинария

- Культура

- Литература

- Математика

- Медицина

- Металлургия

- Мифология

- Музыка

- Психология

- Религия

- Спорт

- Строительство

- Техника

- Транспорт

- Туризм

- Усадьба

- Физика

- Фотография

- Химия

- Экология

- Электричество

- Электроника

- Энергетика

Подключение EROM и ERAM к микроконтроллеру

На рисунке 1.5 приведена типовая схема подключения EROM и ERAM к микроконтроллеру, на рисунках 1.6, 1.7, 1.8 – временные диаграммы сигналов при чтении байта из EROM, ERAM и записи байта в ERAM соответственно.

| |||

| Рисунок 1.5 – Типовая схема подключения EROM и ERAM | |||

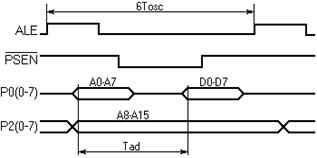

Рисунок 1.6 – Чтение байта из EROM

Рисунок 1.6 – Чтение байта из EROM

| |||

Рисунок 1.7 – Чтение байта из ERAM

Рисунок 1.7 – Чтение байта из ERAM

| |||

| |||

| Рисунок 1.8 – Запись байта в ERAM |

В таблице 1.3 приведены значения параметров, указанных на временных диаграммах.

| Таблица 1.3 – Значения параметров, указанных на временных диаграммах | |||

| Fosc, Мгц | Чтение из EROM | Чтение из ERAM | Запись в ERAM |

| Trd max (нс) | Trd max (нс) | Twr min (нс) | |

| 16-24 | 5Tosc-55 | 9Tosc-165 | 6Tosc-100 |

Параллельные порты ввода–вывода P0 и P2 при подключении к микроконтроллеру внешней памяти (EROM и ERAM) используются для выдачи шестнадцатиразрядного кода адреса, а порт Р0, кроме того, для выдачи и приема байтов данных. Младший байт кода адреса (A0-A7) выдается через порт Р0 и запоминается во внешнем регистре. Запись кода во внешний регистр выполняется при высоком уровне сигнала на выходе ALE. Старший байт кода адреса (А8-А15) выдается через порт Р2 и удерживается на выводах порта Р2 в течение всего времени обращения к внешней памяти.

Чтение байта из EROM происходит при низком уровне сигнала на выходе PSEN, чтение байта из ERAM – при низком уровне сигнала RD на выходе порта Р3.7, а запись байта в ERAM – при низком уровне сигнала WR на выходе порта Р3.6.

Контрольные вопросы

1 Какова емкость внутреннего ОЗУ микроконтроллера? Какая часть адресов используется только для обращения к ячейкам IRAM? К чему может привести некорректное использование старшей половины адресов?

2 Что означает понятие "Банк регистров"? Каким образом осуществляется выбор активного банка регистров?

3 Номера регистров какого банка совпадают с адресами ячеек ОЗУ?

4 К каким ячейкам памяти из старшей половины адресов допускается поразрядное обращение?

5 Каков принцип работы стека LIFO?

6 Какой адрес соответствует дну стека при сбросе микроконтроллера?

7 Изменится ли значение ячейки по адресу 07H при помещении значения в стек сразу же после сброса микроконтроллера?

8 Что необходимо сделать для безопасного использования всех банков регистров при использовании стека?

9 К чему приведет загрузка в указатель стека числа 7FH и дальнейшему использованию стека?

10 Для чего необходим регистр RG на рис. 1.5? Возможно ли программно записать данные в этот регистр, не нарушив обращение к внешней памяти? Почему?

11 Чем отличается подключение внешних памяти программ и памяти данных?

12 Возможно ли одновременное подключение ОЗУ и ПЗУ, емкость каждой из которых 64 кБ.

13 Какая часть адреса удерживается в течение всего цикла обращения к памяти?

Не нашли, что искали? Воспользуйтесь поиском: