ТОР 5 статей:

Методические подходы к анализу финансового состояния предприятия

Проблема периодизации русской литературы ХХ века. Краткая характеристика второй половины ХХ века

Характеристика шлифовальных кругов и ее маркировка

Служебные части речи. Предлог. Союз. Частицы

КАТЕГОРИИ:

- Археология

- Архитектура

- Астрономия

- Аудит

- Биология

- Ботаника

- Бухгалтерский учёт

- Войное дело

- Генетика

- География

- Геология

- Дизайн

- Искусство

- История

- Кино

- Кулинария

- Культура

- Литература

- Математика

- Медицина

- Металлургия

- Мифология

- Музыка

- Психология

- Религия

- Спорт

- Строительство

- Техника

- Транспорт

- Туризм

- Усадьба

- Физика

- Фотография

- Химия

- Экология

- Электричество

- Электроника

- Энергетика

Последовательные устройства типа GAL

Два «управляющих архитектурой» программируемых соединения позволяют выбрать одну из трех основных конфигураций этого устройства. Одна из них конфигурация I6V8C - по своей структуре она похожа на биполярное комбинационное ПЛУ PALI6L8. Конфигурация 16V8S немного отличается от конфигурации 16V8C возможностями комбинационной логики.

Третья конфигурация I6V8R обеспечивает наличие триггеров на всех выходах или на некоторых из них.

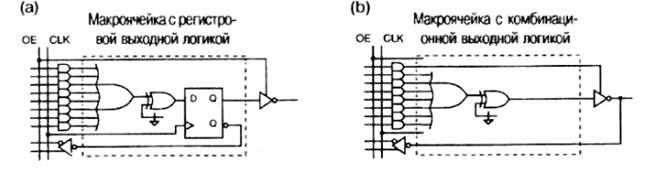

ИС 16 V8R значительно более гибкое устройство, нежели микросхема PALI6R8, поскольку можно по отдельности задавать конфигурацию каждой макроячейки так, чтобы обойти триггер, то есть обеспечить наличие комбинационного выхода. На рис. 8.21 показаны две возможные конфигурации макроячейки в ИС 16V8R: (а) регистровая конфигурация и (Ь) комбинационная конфигурация. Следовательно, устройство можно запрограммировать так, чтобы любой набор выходов был регистровым или комбинационным вплоть до полного числа выходов, равного 8.

Главные отличия ИС 22VI0 от ИС 20V8 состоят в следующем;

• Как и в архитектуре 20V8R, каждую макроячейку выходной логики можно запрограммировать так, чтобы она имела регистровую или комбинационную конфигурацию.

• Один из термов-произведений управляет выходным буфером независимо от того, какая конфигурация выбрана для макроячейки: регистровая или комбинационная.

• Для любого выхода имеется, по меньшей мере, восемь термов-произведений, независимо от выбранной конфигурации макроячейки выходной логики.

• Тактовый сигнал, подаваемый на вывод 1, может играть роль комбинационного входного сигнала в любом терме-произведении.

• Глобальный асинхронный сигнал сброса генерируется в виде одного терма-произведения; с его помощью все внутренние триггеры сбрасываются в 0.

• Глобальный синхронный сигнал установки в единичное состояние генерируется в виде одною терма-произведения; этим сигналом осуществляется перевод всех внутренних триггеров в состояние I, и происходит это на нарастающем фронте тактового сигнала.

• Как и в схемах I6V8 h20V8, полярность выходных сигналов в ИС 22VI0 программируется. Однако в случае регистровой конфигурации изменение полярности осуществляется на выходе D-триггсра, а не на его входе. Это затрагивает некоторые детали программирования, когда необходимо изменить полярность, но не влияет на возможность реализации данной функции микросхемой 22V10 в целом. Различие, обусловленное тем, в каком месте происходит изменение полярности, становится явным при программировании ПЛУ на том или ином языке, например, на языке ABEL.

ИС типа GAL, в том числе GAL16V8 и GAL20V8, впервые были выпушены фирмой Lattice Semiconductor в середине 80-х годов. За этими схемами последовала совместимая с ними по выводам ИС PALCEI6V8 фирмы Advanced Micro Devices. Несколько других производителей также выпускают совместимые устройства, но с другой маркировкой. В этой главе мы называем эти микросхемы их первоначальными именами I6V8,20V8 и 22V10, не ставя себе целью представить в деталях всю номенклатуру различных производителей.

Не нашли, что искали? Воспользуйтесь поиском: