ТОР 5 статей:

Методические подходы к анализу финансового состояния предприятия

Проблема периодизации русской литературы ХХ века. Краткая характеристика второй половины ХХ века

Характеристика шлифовальных кругов и ее маркировка

Служебные части речи. Предлог. Союз. Частицы

КАТЕГОРИИ:

- Археология

- Архитектура

- Астрономия

- Аудит

- Биология

- Ботаника

- Бухгалтерский учёт

- Войное дело

- Генетика

- География

- Геология

- Дизайн

- Искусство

- История

- Кино

- Кулинария

- Культура

- Литература

- Математика

- Медицина

- Металлургия

- Мифология

- Музыка

- Психология

- Религия

- Спорт

- Строительство

- Техника

- Транспорт

- Туризм

- Усадьба

- Физика

- Фотография

- Химия

- Экология

- Электричество

- Электроника

- Энергетика

Другие схемы синхронизирующих устройств

Еще один способ построения более надежного синхронизирующего устройства: увеличение допустимого времени tr в выражении для MTBF.

На рисунке изображена схема многотактного синхронизирующего устройства.

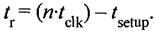

Здесь частота системного тактового сигнала делится на n, полученное таким образом колебание играет роль тактового сигнала для синхронизирующего устройства и допустимое время метастабильности возрастает до  Обычно значения n = 2 или n = 3 обеспечивают подходящую надежность синхронизирующего устройства.

Обычно значения n = 2 или n = 3 обеспечивают подходящую надежность синхронизирующего устройства.

В этой схеме перепады в сигнале CLOCKN будут отставать от перепадов в сигнале CLOCK, поскольку CLOCKN является выходным сигналом счетчика, состоящего из триггеров, переключающихся по фронту сигнала CLOCK. Это означает, что сигнал SYNC1N, в свою очередь, будет задержан или затянут по отношению к другим сигналам в синхронной системе, которые вырабатываются триггерами, переключающимися по фронту сигнала CLOCK непосредственно. Если сигнал SYNC IN проходит в синхронной системе через дополнительную комбинационную логику, прежде чем достигает входов системных триггеров, то требования, предъявляемые временем установления этих триггеров, могут оказаться невыполненными.

Чем больше n в n-тактном синхронизирующем устройстве, тем дольше синхронной системе не видно изменение асинхронного входного сигнала. Эта задержка является ценой, которую необходимо уплатить за надежную работу системы. В типичной микропроцессорной системе большая часть асинхронных входных сигналов извещает систему о внешних событиях (прерывания, требования прямого доступа в память и т.д.), так что не требуется распознавать их очень быстро с точки зрения задержки в синхронизирующем устройстве. Когда обращение к памяти критично по времени, опытные разработчики заставляют подсистему памяти работать от тактового сигнала процессора, если только это возможно. При этом надобность в синхронизирующем устройстве пропадает и система функционирует с наибольшим возможным быстродействием.

На более высоких частотах возможность реализации многотактного синхронизирующего устройства по схеме, приведенной на рис. 1, ограничена разбросом задержек тактового сигнала. По этой причине некоторые проектировщики вместо деления частоты системного тактового сигнала на п применяют последовательно включенные синхронизирующие устройства. При таком подходе используется цепочка из п триггеров (регистр сдвига), в которой все триггеры переключаются быстрым системным тактовым сигналом. Соответствующая схема показана на рис. 2

Принцип действия многокаскадного синхронизирующего устройства основан на том, что с некоторой вероятностью выход из состояния метастабильности произойдет уже в первом триггере, а в случае неудачи - с равной вероятностью в каждом следующем из триггеров, включенных последовательно. Таким образом, вероятность отказа синхронизирующего устройства в целом оказывается порядка п-й степени вероятности отказа на данной частоте системного тактового сигнала синхронизирующего устройства с одним триггером. И хотя это отчасти верно, все же величина MTBF для многокаскадного синхронизирующего устройства меньше, чем для многотактного синхронизирующего устройства с тем же временем задержки (wclk). В случае многокаскадного устройства время установления триггера t необходимо вычесть п раз из времени t, тогда как в случае многотактного устройства значение ts вычитается только один раз.

Для построения синхронизирующего устройства можно воспользоваться внутренними триггерами ПЛУ. Однако, значение MTBF для синхронизирующего устройства, образованного внутри ПЛУ, хуже, чем при использовании отдельных ИС, созданных по той же или подобной технологии. Это происходит потому, что на D-входе каждого триггера в ПЛУ имеется комбинационная логическая матрица, увеличивающая его время установления и тем самым уменьшающая время / в течение которого должен произойти выход из состояния метастабильности.

Не нашли, что искали? Воспользуйтесь поиском: