ТОР 5 статей:

Методические подходы к анализу финансового состояния предприятия

Проблема периодизации русской литературы ХХ века. Краткая характеристика второй половины ХХ века

Характеристика шлифовальных кругов и ее маркировка

Служебные части речи. Предлог. Союз. Частицы

КАТЕГОРИИ:

- Археология

- Архитектура

- Астрономия

- Аудит

- Биология

- Ботаника

- Бухгалтерский учёт

- Войное дело

- Генетика

- География

- Геология

- Дизайн

- Искусство

- История

- Кино

- Кулинария

- Культура

- Литература

- Математика

- Медицина

- Металлургия

- Мифология

- Музыка

- Психология

- Религия

- Спорт

- Строительство

- Техника

- Транспорт

- Туризм

- Усадьба

- Физика

- Фотография

- Химия

- Экология

- Электричество

- Электроника

- Энергетика

Статические D-тригеры.

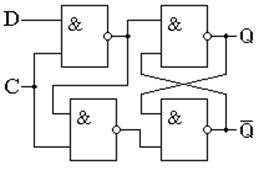

В RS‑триггерах для записи логического нуля и логической единицы требуются разные входы, что не всегда удобно. При записи и хранении данных один бит может принимать значение, как нуля, так и единицы. Для его передачи достаточно одного провода. Как мы уже видели ранее, сигналы установки и сброса триггера не могут появляться одновременно, поэтому можно объединить эти входы при помощи инвертора, как показано на рисунке 8.7.

Рисунок 8.7 – Схема D‑триггера

Такой триггер получил название D‑триггер (защелка). Название происходит от английского слова delay – задержка. Конкретное значение задержки определяется частотой следования импульсов синхронизации. Условно-графическое обозначение D‑триггера на принципиальных схемах приведено на рисунке 8.8.

Рисунок 8.8 – Условно-графическое обозначение D‑триггера

Таблица истинности D‑триггера достаточно проста, она приведена в таблице 8.3. Как видно из этой таблицы, D‑триггер способен запоминать по синхросигналу и хранить один бит информации.

Таблица 8.3 – Таблица истинности D‑триггера

| С | D | Q(t) | Q(t+1) | Пояснения |

| x | Режим хранения информации | |||

| x | ||||

| x | Режим записи информации | |||

| x |

Следует отметить, что отдельный инвертор при реализации триггера на ТТЛ элементах не используется, так как самый распространённый элемент ТТЛ логики – это элемент "2И‑НЕ". Принципиальная схема D‑триггера на элементах "2И‑НЕ" приведена на рисунке 8.9.

Рисунок 8.9 – Схема D‑триггера, реализованная на ТТЛ элементах

Ещё проще реализуется D‑триггер на КМОП логических элементах. В КМОП микросхемах вместо логических элементов "И" используются обычные транзисторные ключи. Схема D‑триггера приведена на рисунке 8.10.

Рисунок 8.10 – Схема D‑триггера, реализованная на КМОП элементах

При подаче высокого уровня синхросигнала C транзистор VT1 открывается и обеспечивает передачу сигнала с входа D на инверсный выход Q через инвертор D1. Транзистор VT2 при этом закрыт и отключает второй инвертор, собранный на транзисторах VT2 и VT3. При подаче низкого потенциала на вход C включается второй инвертор, который вместе с инвертором D1 и образует триггер.

Во всех рассмотренных ранее схемах синхронных триггеров синхросигнал работает по уровню, поэтому триггеры называются триггерами, работающими по уровню. Ещё одно название таких триггеров, пришедшее из зарубежной литературы – триггеры-защёлки. Легче всего объяснить появление этого названия по временной диаграмме, приведенной на рисунке 8.11.

Рисунок 8.11 – Временная диаграмма D триггера

По этой временной диаграмме видно, что триггер-защелка хранит данные на выходе только при нулевом уровне на входе синхронизации. Если же на вход синхронизации подать активный высокий уровень, то напряжение на выходе триггера будет повторять напряжение, подаваемое на вход этого триггера. Входное напряжение запоминается только в момент изменения уровня напряжения на входе синхронизации C с высокого уровня на низкий уровень. Входные данные как бы "защелкиваются" в этот момент, отсюда и название – триггер-защелка. Принципиально в этой схеме входной переходной процесс может беспрепятственно проходить на выход триггера. Поэтому там, где это важно, необходимо сокращать длительность импульса синхронизации до минимума. Чтобы преодолеть такое ограничение были разработаны триггеры, работающие по фронту.

Не нашли, что искали? Воспользуйтесь поиском: