ТОР 5 статей:

Методические подходы к анализу финансового состояния предприятия

Проблема периодизации русской литературы ХХ века. Краткая характеристика второй половины ХХ века

Характеристика шлифовальных кругов и ее маркировка

Служебные части речи. Предлог. Союз. Частицы

КАТЕГОРИИ:

- Археология

- Архитектура

- Астрономия

- Аудит

- Биология

- Ботаника

- Бухгалтерский учёт

- Войное дело

- Генетика

- География

- Геология

- Дизайн

- Искусство

- История

- Кино

- Кулинария

- Культура

- Литература

- Математика

- Медицина

- Металлургия

- Мифология

- Музыка

- Психология

- Религия

- Спорт

- Строительство

- Техника

- Транспорт

- Туризм

- Усадьба

- Физика

- Фотография

- Химия

- Экология

- Электричество

- Электроника

- Энергетика

ОПЕРАЦИОННЫЕ УСИЛИТЕЛИ

Термин «операционный усилитель» относится к усилителям постоянного тока с большим коэффициентом усиления, имеющим дифференциальный вход(два входных вывода) и один общий выход (один вывод). Название этих усилителей связано с первоначальным их применением главным

|

образом для выполнения различных операций над аналоговыми величинами (сложение, вычитание, интегрирование и др.). Однако благодаря достижениям в области микроэлектроники и широкому выпуску операционных усилителей в интегральном исполнении открылись их более широкие схемотехнические возможности. В настоящее время операционные усилители (ОУ) играют роль многоцелевых элементов при построении аппаратуры самого различного назначения. Они применяются в усилительной технике, устройствах генерации сигналов синусоидальной и импульсной форм, в стабилизаторах напряжения, активных фильтрах и т. д.

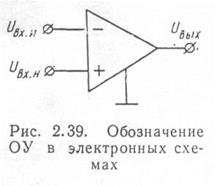

Условное обозначение ОУ показано на рис. 2.39. Один из входов усилителя Uвх.н, «+») называется неинвертирующим, а второй (Uвх.и, «-») -инвертирующим. При подаче сигнала на неинвертирующий вход приращение выходного сигнала совпадает по знаку (фазе) с приращением входного сигнала. Если же сигнал подан на инвертирующий вход, то приращение выходного сигнала имеет обратный знак (противоположный по фазе) по сравнению с приращением входного сигнала. Инвертирующий вход часто используют для введения в операционный усилитель внешних отрицательных, обратных связей.

Основу ОУ составляет дифференциальный каскад, применяемый в качестве входного каскада усилителя. Выходным каскадом ОУ обычно служит эмиттерный повторитель (ЭП), обеспечивающий требуемую нагрузочную способность всей схемы. Поскольку коэффициент усиления по напряжению эмиттерного повторителя близок к единице, необходимое значение КUоу операционного усилителя достигается с помощью дополнительных усилительных каскадов, включаемых между дифференциальным каскадом и ЭП. В зависимости от количества каскадов, используемых для получения требуемого значения КUоу, ОУ подразделяют на двух- и трехкаскадные.

В двухкаскадных ОУ в усилении входного сигнала участвуют входной дифференциальный каскад и один дополнительный каскад,

|

а в трехкаскадных — входной дифференциальный и два дополнительных каскада. В трехкаскадных ОУ входной дифференциальный каскад обычно выполняют с резистивными нагрузками, а в двухкаскадных — с динамическими нагрузками. Помимо этого, операционные усилители могут содержать вспомогательные транзисторные каскады и элементы, предназначенные, например, для сдвига уровней напряжения в тракте усиления, создания источников стабильного тока, отрицательных обратных связей по синфазным ошибкам усиления и.т. д.

Для иллюстрации рассмотрим принципиальную схему простейшего трехкаскадного ОУ, приведенную на рис. 2.40 (микросхема 14ОУД1). Питание схемы осуществляется от двух источников +Ек1 и — Ек2 с одинаковым напряжением. Источники питания имеют общую точку: |Ек1| = |Ек2| = Ек.

Входной усилительный каскад выполнен на транзисторах Ти Т2 по дифференциальной схеме рис. 2.33, а. Выходы первого каскада связаны с входами второго каскада на транзисторах Т5, Т6 также по дифференциальной схеме. Резистор в цепи коллектора транзистора Т5 отсутствует, так как выходной сигнал второго каскада снимается только с коллектора транзистора Т6. Источник стабильного тока во втором дифференциальном каскаде не используется. Требуемая стабильность суммарного тока Iэ транзисторов Т5, Т6 достигается с помощью резистора Rэ = R5. Падение напряжения на резисторе R5 от протекания тока Iэ обоих транзисторов повышает потенциал их эмиттеров, что необходимо для непосредственной связи баз транзисторов с выходами предыдущего каскада.

Третий усилительный каскад выполнен на транзисторах Т7, Т8. Выход его связан с входом транзистора Т9, на котором реализован выходной эмиттерный повторитель. Построение третьего усилительного каскада таково, что транзисторы Т7, Т8 представляют собой как бы управляемые элементы входного делителя эмиттерного повторителя. Управление транзистором Г7 производится по цепи базы выходным сигналом второго каскада, управление транзистором Т8 — по цепи эмиттера напряжением на резисторе R12, создаваемым от протекания через этот резистор тока эмиттера транзистора Т9. Транзистор Т8 входит в контур положительной обратной связи, позволяющей обеспечить высокий коэффициент усиления третьего каскада. Совместное действие транзисторов T7 и T8 направлено либо на увеличение, либо на уменьшение (в зависимости от сигнала на входе транзистора Т6) входного напряжения эмиттерного повторителя, т. е. потенциала базы транзистора Т9 относительно шины —Eк2. Повышение напряжения на базе транзистора T9 обусловливается уменьшением сопротивления постоянному току транзистора Т7, а также увеличением сопротивления транзистора T8, и наоборот.

Рассмотрим характер изменения выходного напряжения ОУ при изменении сигнала на базе транзистора Т7.

При входных напряжениях ОУ Uвх.н = Uвх.и =0 напряжение на коллекторе транзистора Т6 таково, что близкие по величине потенциалы базы и эмиттера транзистора Т9 относительно шины — Ек2 равны + Ек и напряжение на выходе ОУ Uвых =0.

Если под действием входных сигналов (показанных на рис. 2.40 в виде полуволн) напряжение на коллекторе транзистора Т6 увеличится (положительная полуволна), то увеличатся также токи Iб, Iэ транзистора Т7. Это приводит к увеличению токов Iб, Iэ транзистора. Напряжение на резисторе R12 повышается, что уменьшает напряжение Uбэ и токи Iб и Iк транзистора Т8. Ввиду возрастания тока Iэ транзистора Т7 и уменьшения тока Iк транзистора Т8 потенциалы базы и эмиттера транзистора Т9 относительно шины — Ек2 становятся больше +Ек. На выходе усилителя создается напряжение положительной полярности Uвых > 0 (на рис. 2.40 показана без скобок).

При снижении напряжения на коллекторе транзистора T6 токи транзисторов Т7, T9 уменьшаются, а токи транзистора Т8 увеличиваются. Это приводит к уменьшению потенциалов базы и эмиттера транзистора T9 относительно шины — Eк2, на выходе усилителя будет действовать напряжение отрицательной полярности Uвых < 0 (на рис. 2.40 показана в скобках).

Очевидно, максимальное выходное напряжение U- выхmax отрицательной полярности будет близко к -Ек2 = —Ек а максимальное напряжение положительной полярности U+ выхmax — к + Ек1 = + Ек. Реакцию усилителя на воздействие входных сигналов легко проследить, рассмотрев прохождение усиливаемого сигнала по всему тракту усиления (как показано на рис. 2.40, например, при подаче положительной полуволны напряжения на неинвертирующий вход при заземленном инвертирующем входе).

Операционные усилители характеризуются усилительным и, входными, выходными, энергетическими, дрейфовыми, частотными и скоростными параметрами. Рассмотрим наиболее существенные из них.

Важнейшими характеристиками ОУ являются его амплитудные (передаточные) характеристики (рис. 2.41). Их представляют в виде двух кривых, относящихся соответственно к инвертирующему и неинвертирующему входам. Характеристики снимают при подаче сигнала на один из входов при нулевом сигнале на другом. Каждая из кривых состоит из горизонтальных и наклонного участков.

Горизонтальные участки кривых соответствуют режиму полностью открытого (насыщенного) либо закрытого транзистора выходного

|

каскада (эмиттерного повторителя). При изменении напряжения входного сигнала на этих участках выходное напряжение усилителя остается без изменения и определяется

напряжениями U+ выхmax, U- выхmax.

Указанные значения максимальных выходных напряжений близки к напряжению Ек источников питания. Наклонному (линейному) участку кривых соответствует пропорциональная зависимость выходного напряжения от входного. Угол наклона участка определяется коэффициентом усиления КUоу =∆ Uвых/ ∆ Uвх операционного усилителя.

Значение КUоу зависит от типа ОУ и может составлять от нескольких сотен до сотен тысяч и более. Большие значения КUоу позволяют при охвате таких усилителей глубокой отрицательной обратной связью получать схемы со свойствами, которые зависят только от параметров цепи отрицательной обратной связи.

Кривые, приведенные на рис. 2.41, проходят через нуль. Состояние, когда Uвых = 0 при Uвх = 0, называется балансом ОУ. Однако для реальных ОУ условие баланса обычно не выполняется (наблюдается разбаланс). При Uвх = 0 выходное напряжение ОУ может быть больше или меньше нуля (Uвых = + ∆ Uвых или Uвых = - ∆ Uвых). На Рис. 2.42 пунктирными линиями показан возможный вид передаточной характеристики реальных ОУ привходном сигнале, подаваемом на неинвертирующий вход. Напряжение Uсм0, при котором Uвых = 0, называется входным напряжением смещения нуля. Оно определяет значение напряжения, которое необходимо подать на вход ОУ для создания баланса. Напряжения Uсм0 и ∆ Uвых связаны соотношением Uсm0 =∆ Uвых/Кuоу. Основной причиной разбаланса ОУ является существующий разброс параметров элементов дифференциального усилительного каскада (в частности, транзисторов). Зависимость от температуры параметров ОУ вызывает температурный дрейф входного напряжения смещения и температурный дрейф выходного напряжения.

Входное сопротивление, входные токи смещения, разность и дрейф входных токов смещения, а также максимальное входное дифференциальное напряжение характеризуют основные параметры, входных

цепей операционных усилителей, которые, в свою очередь, зависят от схемы используемого дифференциального входного каскада. Наличие входных токов смещения обусловливается конечным значением входного сопротивления дифференциального каскада, а их разность — существующим разбросом параметров транзисторов (различием начальных входных токов смещения). Начальные входные токи смещения ОУ с дифференциальным кас-

цепей операционных усилителей, которые, в свою очередь, зависят от схемы используемого дифференциального входного каскада. Наличие входных токов смещения обусловливается конечным значением входного сопротивления дифференциального каскада, а их разность — существующим разбросом параметров транзисторов (различием начальных входных токов смещения). Начальные входные токи смещения ОУ с дифференциальным кас-

|

кадом на биполярных транзисторах определяются токами баз транзисторов при заземленных входах (базовыми токами транзисторов в режиме покоя), а при наличии каскадов на полевых транзисторах — токами утечек затворов.

Необходимость учета входных токов возникает при построении схем на ОУ, когда в цепь одного или обоих его входов включаются резисторы (рис. 2.43). При неодинаковых величинах сопротивлений резисторов или входных токов падения напряжения на резисторах R1 и R2 будут неодинаковыми» что создает между входами дифференциальное напряжение и соответственно вызывает появление на выходе некоторого напряжения (разбаланса). Ввиду наличия входного напряжения смещения и входных токов смещения схемы на ОУ приходится дополнять элементами, предназначенными для начальной их балансировки. Балансировка осуществляется путем подачи на один из входов ОУ некоторого дополнительного напряжения и введения резисторов в его входные цепи.

Максимальным дифференциальным входным напряжением лимитируется напряжение, подаваемое между входами ОУ в схеме, для исключения повреждения транзисторов дифференциального каскада. Для защиты между входами ОУ включают встречно-параллельно два диода или стабилитрона.

Наличие синфазного напряжения на входах ОУ вызывает появление выходной синфазной ошибки усиления. Так же как и для дифференциального каскада (см. § 2.7), влияние синфазного входного напряжения оценивают коэффициентом ослабления синфазного сигнала (КОСС).

Выходными параметрами ОУ являются выходное сопротивление, а также максимальное выходное напряжение и ток. ОУ должен обладать малым выходным сопротивлением для обеспечения высоких значений напряжения на выходе при малых сопротивлениях нагрузки. Малое выходное сопротивление (десятки и сотни ом) достигается применением на выходе ОУ эмиттерного повторителя. Максимальное выходное напряжение

|

|

(положительное и отрицательное), как указывалось, близко к напряжению питания Eк = Eк1 = Ек2, которое может составлять 3—15 В. Максимальный выходной ток ограничивается допустимым коллекторным током выходного каскада ОУ. Энергетические параметры ОУ оценивают максимальными потребляемыми токами от обоих источников питания и соответственно с у м марной потребляемой мощностью.

Усиление гармонических сигналов характеризуется частотными параметрами ОУ, а усиление импульсных сигналов — его скоростными или динамическими параметрами.

Частотные параметры определяют по амплитудно-частотной характеристике ОУ (рис. 2.44, а), которая имеет спадающий характер в области высокой частоты, начиная от частоты среза fср. Причиной этого является частотная зависимость параметров транзисторов и паразитных емкостей схемы ОУ. Частота f1 при которой коэффициент усиления ОУ равен единице, называется частотой единичного усиления. По граничной частоте fвп, которой соответствует снижение коэффициента усиления ОУ в  раз, оценивают полосу-пропускания частот усилителя, составляющую для современных ОУ десятки мегагерц.

раз, оценивают полосу-пропускания частот усилителя, составляющую для современных ОУ десятки мегагерц.

При усилении сигналов ОУ обычно охватывается отрицательной обратной связью по инвертирующему входу. Ввиду создаваемого усилителем в области высоких частот фазового сдвига выходного сигнала относительно входного фазо-частотная характеристика ОУ по инвертирующему входу приобретает дополнительный (сверх 180°) фазовый сдвиг (рис. 2.44, б). Для некоторой высокой частоты полный фазовый сдвиг становится равным 360º, что соответствует положительной обратной связи по инвертирующему входу на этой частоте. Это приводит к самовозбуждению схемы. Для устранения самовозбуждения в ОУ вводят внешние корректирующие RС -цепи, позволяющие несколько изменить ход амплитудно-частотной и фазо-час-тотной характеристик. Параметры RC-цепей и места их подсоединения к микросхеме (для исключения самовозбуждения) указываются заводом-изготовителем.

Динамическими параметрами ОУ являются скорость нарастания выходного напряжения (скорость отклика) и время установления выходного напряжения. Они определяются по реакции ОУ на воздействие скачка напряжения на входе (рис. 2.45, а, б). Скорость нарастания выходного напряжения vUвых находят по отношению приращения выходного напряжения к времени на участке изменения выходного напряжения от 0,1 Uвых до 0,9 Uвых. Время установления выходного напряжения tycт оценивают интервалом времени, в течение которого выходное напряжение изменяется от уровня 0,1 до уровня 0,9 установившегося значения. Ряд схем ОУ допускают введение корректирующих цепей, улучшающих параметры vUвых и tуст. Для ОУ vUвых =0,1 ―100 В/мкс, a tycт =0,05 ―2 мкс.

Широкое практическое использование ОУ в аналоговых схемах основывается главным образом на применении в них различного рода внешних отрицательных обратных связей, чему способствует большое значение коэффициента усиления КUоу, а также высокое входное и малое выходное сопротивления ОУ. Высокие качества параметров современных ОУ позволяют, в частности, без внесения заметной погрешности при расчете схем на ОУ принимать КUоу→∞, К10у→∞ и Rв хОУ →∞.

Рассмотрим некоторые примеры построения аналоговых схем на ОУ, режим работы которого осуществляется в пределах линейного участка передаточных характеристик.

|

Инвертирующий усилитель. Инвертиру-ющий усилитель (рис. 2.46), изменяющий знак выходного сигнала относительно входного, Создается введением по инвертирующему входу ОУ с помощью резистора Roc параллельной отрицательной обратной связи по напряжению. Неинвертирующий вход связывается с общей точкой входа и выхода схемы (заземляется). Входной сигнал подается через резистор R1 на инвертирующий вход ОУ.

Показатели схемы можно определить, воспользовавшись уравнением токов для узла 1. Если принять RвхОУ =∞ и входной ток ОУ Iоу = 0, то Iвх = Iос, откуда

(Uвх- U0)/R1 =-(Uвых-U0)/Roc (2.138)

При КUоу→ ∞напряжение на входе ОУ U0 = Uвыx/KUoy →0, в связи с чем выражение (2.138) принимает вид

Uвх/R1=- Uвых/Roc (2.139)

Следовательно, коэффициент усиления по напряжению инверти-рующего усилителя с параллельной обратной связью КUи = = Uвыx / Uвх определяется параметрами только пассивной части схемы:

КUи=—Rос/R1 (2.140)

Выбор Roc = R1, когда КUи = -1 придает схеме рис. 2.46 свойство инвертирующего повторителя напряжения (инвертора сигнала). Поскольку Uо→ 0, входное сопротивление схемы Rвх =R1. Выходное сопротивление усилителя

Rвых = RвыхОУ(1+Roc/R1)/ KUoy (2.141)

при KUoy близко к нулю.

Неинвертирующий усилитель. Неинвертирующий усилитель (рис. 2.47) содержит последовательную отрицательную обратную связь по напряжению, поданную по инвертирующему входу; входной сигнал подается на неинвертирующий вход ОУ.

В силу равенства нулю напряжения между входами ОУ (U0 =0) входное напряжение схемы связано с выходным напряжением соот-ношением

В силу равенства нулю напряжения между входами ОУ (U0 =0) входное напряжение схемы связано с выходным напряжением соот-ношением

откуда коэффициент усиления неинвертирующего усилителя

откуда коэффициент усиления неинвертирующего усилителя

(2.142)

|

|

|

При Roc =0 и R1 =∞ приходим к схеме повторителя (рис. 2.48) с КU =1.

Входное сопротивление неинвертирующего усилителя RBX, равное входному сопротивлению ОУ по неинвертирующему входу, велико; выходное сопротивление Rвых→ 0. Его находят из соотношения (2.141).

Неинвертирующий и инвертирующий усилители широко используют в качестве высокостабильных усилителей различного назначения.

Преобразователь тока в напряжение. Схема, осуществляющая преобразование тока в напряжение (рис. 2.49), является вариантом

|

|

схемы рис. 2.46 при R1 = 0. Из схемы рис. 2.49 имеем

Iвх = Iос =-Uвых/Rос,

откуда

Uвых=-IвхRос (2.143)

Малые входное и выходное сопротивления являются важными преимуществами схемы при ее использовании для преобразования тока источников сигнала в напряжение.

Инвертирующий сумматор. Схема рис. 2.50 выполняется по типу инвертирующего усилителя (см. рис. 2.46) с числом параллельных ветвей на входе, равным количеству сигналов, предназначенных для сложения. Сопротивления резисторов принимают одинаковыми:

Roc=R1=R2=…=Rn<<RвхОУ.

При IвхОУ = 0 имеем

Ioc=I1+I2+…+In

или

Uвых=-(U1+U2+…+Un) (2.144)

Соотношение (2.144) отражает равноправное весовое участие слагаемых в их сумме. Суммирование может производиться и с соответствующими весовыми коэффициентами для каждого из слагаемых:

это достигается применением различных значений сопротивлений резисторов во входных ветвях.

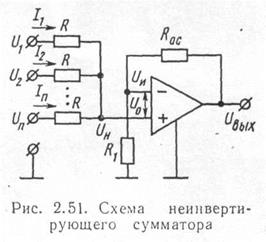

Неинвертирующий сумматор. Неинвертирующий сумматор может быть реализован путем последовательного соединения схемы рис. 2.50 и инвертора (см. рис. 2.46). Однако он выполняется проще (рис. 2.51) на основе схемы рис. 2.47.

При U0 = 0 (рис. 2.51) напряжения на обоих входах ОУ равны

и составляют Uн == Uи =  . При равенстве нулю тока по неинвертирующему входу (RвхOy =∞) имеем

. При равенстве нулю тока по неинвертирующему входу (RвхOy =∞) имеем

или

U1+U2+…+Un=n  ,

,

откуда

Uвых=  (2.145)

(2.145)

Выбор параметров схемы производят, исходя из равенства единице первого сомножителя в правой части выражения (2.145):

(R1 + Roc)/(nR1) = 1

Интегратор. Схема интегратора (рис. 2.52, а) создается заменой в схеме рис. 2.46 резистора Roc конденсатором. По аналогии со схемой рис.2.46, ic = iR. Тогда

,

,

(2.146)

где Uвых0 — выходное напряжение при t = 0.

Отсчет времени ведут с момента поступления входного сигнала, причем обычно при t = 0 ивх=0 и uвых = 0. В связи с указанным выражение (2.146) приобретает вид

Отсчет времени ведут с момента поступления входного сигнала, причем обычно при t = 0 ивх=0 и uвых = 0. В связи с указанным выражение (2.146) приобретает вид

(2.147)

где τ = RC — постоянная интегрирования.

При τ = RC = 1с-1 (например, R = 1 мОм и С = 1 мкФ) интегрирование осуществляется в реальном масштабе времени. При других соотношениях R и С масштаб интегрирования может быть иным. Так, при R= 1 мОм и С=0,1 мкФ τ =0,1 с-1 и масштаб интегрирования во времени составляет 10.

Масштаб интегрирования выбирают с учетом параметров входных сигналов, чтобы к концу проведения этой операции выходное напряжение усилителя не достигло предельного значения U+вых max или U-вых max В противном случае интегрирование будет выполнено неверно. Указанное иллюстрирует рис. 2.52, б, где входной сигнал представлен в виде единичного скачка напряжения, а выходное напряжение интегратора при неправильном выборе постоянной интегрирования показано пунктиром.

Интегратор широко используют при построении аналоговых решающих и моделирующих устройств. На его основе выполняют генераторы линейно изменяющегося напряжения. При входном импульсе напряжения положительной полярности на выходе такого генератора на базе схемы рис. 2.52, а создается линейно нарастающее напряжение отрицательной полярности или положительной при управлении импульсом напряжения отрицательной полярности. Процесс последующего уменьшения выходного напряжения до нуля (штрихпунктир на рис. 2.52, б) обусловливается разрядом конденсатора с постоянной времени τ = C(R + RвыхОУ). Для уменьшения времени разряда до нуля разряд конденсатора часто осуществляют через включаемый параллельно ему транзисторный ключ (см. гл. 3).

Не нашли, что искали? Воспользуйтесь поиском: