ТОР 5 статей:

Методические подходы к анализу финансового состояния предприятия

Проблема периодизации русской литературы ХХ века. Краткая характеристика второй половины ХХ века

Характеристика шлифовальных кругов и ее маркировка

Служебные части речи. Предлог. Союз. Частицы

КАТЕГОРИИ:

- Археология

- Архитектура

- Астрономия

- Аудит

- Биология

- Ботаника

- Бухгалтерский учёт

- Войное дело

- Генетика

- География

- Геология

- Дизайн

- Искусство

- История

- Кино

- Кулинария

- Культура

- Литература

- Математика

- Медицина

- Металлургия

- Мифология

- Музыка

- Психология

- Религия

- Спорт

- Строительство

- Техника

- Транспорт

- Туризм

- Усадьба

- Физика

- Фотография

- Химия

- Экология

- Электричество

- Электроника

- Энергетика

Схемное построение на эмиттерно-связанных транзисторах

Широкое распространение в аналоговых схемах находит схемное построение рис. 6.8, а. Основной составной частью этого построения является эмиттерно-связанная пара транзисторов VT1 и VT2c идентичными (согласованными) характеристиками. На базе этой конфигурации реализуются не только схемы усиления, но и устройства перемножения сигналов, регулирования усиления, функционального преобразования. Эта конфигурация является основным звеном большинства усилителей постоянного тока, трактов, построенных по так называемой дифференциальной (симметричной) схеме.

Типовое построение рассматриваемой схемы (см. рис. 6.8, а) предполагает использование двух разнополярных источников питания с подключением базовых выводов транзисторов на постоянном токе к точке нулевого потенциала. В силу симметрии схемы в ней в коллекторно-эмиттерных цепях транзисторов протекают одинаковые токи. При этом

Iэ01=Iэ02=I0/2; Ik01=Ik02=I0/2

В качестве основного токозадающего источника, определяющего ток I0 и соответственно исходные значения токов Iк01 и I к02, выступает источник Е„_, выходное напряжение U0;

I0=(-0.7- Еп-)/R0

В ряде случаев построение схемы отличается от типового рис. 6.8, а. Часто базовые выводы транзисторов подключаются к точкам с ненулевым значением постоянного потенциала, например к средней точке резистивных делителей. Такая ситуация наблюдается при питании схемы от одного источника питания (рис. 6.8, б), а также в многокаскадных усилительных трактах, когда в их состав входят несколько непосредственно связанных каскадов. В этих случаях особое внимание обращается на обеспечение схемы на постоянном токе, которая достигается строгим выравниванием токозадающих потенциалов U01 и U02. Необходимость выполнения условия симметрии связана с тем, что рассматриваемая схема весьма чувствительна к разности потенциалов ΔU{) = U01 - U02. Возникновение этой разности потенциалов хотя и не приводит к изменению тока I0, но вызывает его перераспределение между эмиттерными цепями транзисторов. В результате ток одного транзистора увеличивается, а другого — уменьшается. Появление разности потенциалов ΔUQ в 70...80 мВ вызывает практически полную асимметрию в работе схемы на постоянном токе, при которой один транзистор оказывается закрытым, а другой — в состоянии насыщения, вследствие чего схема полностью теряет усилительные свойства. Рассмотрим влияние разности потенциалов ΔU0 на распределение тока I0 между транзисторами.

Ik1=I0/[1+exp(ΔU0/UТ)]; Ik2=I0/[1+exp(-ΔU0/UТ)]

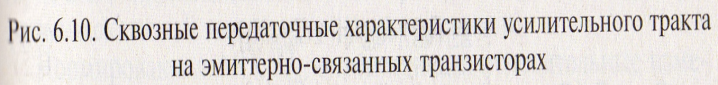

Снижение влияния различия ΔU0 потенциалов базовых цепей может быть достигнуто как за счет охвата усилительного тракта общей петлей ООС, действующей на постоянном токе, так и с помощью дополнительных резисторов RF, включенных в эмиттерные выводы транзисторов (рис. 6.9). Схемные построения при RF≠0 обладают СПХ с повышенной линейностью. Сказанное иллюстрирует рис. 6.10 Линеаризирующее влияние резисторов RF тем больше, чем больше отношение URF/UT (приведенный на рис. 6.10 график соответствует URF/UT = 1,5, т.е. URF~ 40 мВ). Но следует иметь в виду, что увеличение сопротивления RF вызывает снижение усилительных свойств в (1 + g21RF) раз.

Не нашли, что искали? Воспользуйтесь поиском: