ТОР 5 статей:

Методические подходы к анализу финансового состояния предприятия

Проблема периодизации русской литературы ХХ века. Краткая характеристика второй половины ХХ века

Характеристика шлифовальных кругов и ее маркировка

Служебные части речи. Предлог. Союз. Частицы

КАТЕГОРИИ:

- Археология

- Архитектура

- Астрономия

- Аудит

- Биология

- Ботаника

- Бухгалтерский учёт

- Войное дело

- Генетика

- География

- Геология

- Дизайн

- Искусство

- История

- Кино

- Кулинария

- Культура

- Литература

- Математика

- Медицина

- Металлургия

- Мифология

- Музыка

- Психология

- Религия

- Спорт

- Строительство

- Техника

- Транспорт

- Туризм

- Усадьба

- Физика

- Фотография

- Химия

- Экология

- Электричество

- Электроника

- Энергетика

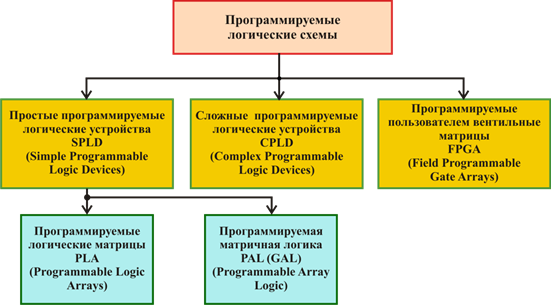

Структура программируемых логических матриц и программируемой матричной логики

Первыми представителями микросхем с программируемыми структурами явились программируемые логические матрицы и программируемая матричная логика.

Как уже было отмечено выше основы микросхем этого вида составляют программируемая матрица элементов И и набор элементов ИЛИ, ко входам которых подключены выходы матрицы И. В их состав входят также блоки входных и выходных буферных каскадов (рисунок 6).

Рисунок 6

Входной буферный каскад, если не предназначен для выполнения более сложных действий, предназначен для преобразования входных сигналов в два один из которых прямой, а другой инверсный. Кроме того входной буферный каскад усиливает преобразованные сигналы до уровня необходимого для нормальной работы элементов матрицы И. С выхода матрицы И снимается l термов (t1 … tl). Под термом здесь понимается конъюнкция, связывающая входные переменные, представленные в прямой или инверсной форме. Число формируемых термов равно числу коньюнкторов или, что то же самое, числу выходов матрицы И.

Термы подаются далее на вход матрицы ИЛИ, то есть на входы дизъюнкторов, формирующих выходные функции. Число дизъюнкторов равно числу вырабатываемых функций n. Выходные буферные каскады обеспечивают необходимую нагрузочную способность выходов, разрешают или запрещают, с помощью сигнала ОЕ (Output Enable), прохождение сигналов на выход, а нередко выполняют и более сложные действия, в частности, программируются на передачу сигналов в прямом или инвертированном виде.

В схеме, представленной на рисунке 7 крестиками в пересечениях горизонтальных и вертикальных линий обозначены программируемые точки связей. После программирования в зависимости от наличия или отсутствия соединений в тех или иных программируемых точках связи формируются необходимые термы, из которых далее составляются требуемые функции.

Рисунок 7

Таким образом, программируемая логическая матрица реализует дизъюнктивную нормальную форму (ДНФ) воспроизводимых функций, то есть представляет их в виде логической суммы логических произведений. Программируемая логическая матрица способна реализовать систему логических функций от m аргументов, содержащую не более l термов. Воспроизводимые функции – комбинации из любого числа термов, формируемых матрицей И. Какие именно термы будут выбраны и какие комбинации этих термов составят выходные фунции, определяется программированием. Некоторые типы микросхем программируемых логических матриц и их основные параметры приведены в таблице 1

Таблица 1

| Микросхема | Число входов | Количество термов | Задержка, нс | Напряжение питания, В |

| PLUS153B/D | 32 логических 10 управляющих | 12 - 15 | +5 | |

| PLUS173B/D | 32 логических 10 управляющих | 12 - 15 | +5,5 | |

| TIB82S167BC | 8 - 20 | +5 |

Схемы программируемых логических матриц достаточно громоздки, поэтому изображать их желательно с максимально возможным упрощением.

Для этого используются изображения, в которых многовходовые элементы И, ИЛИ условно заменяются одновходовыми.

Единственная линия входа таких элементов пересекается с несколькими линиями входных переменных. Если пересечение отмечено точкой, данная переменная подается на вход изображаемого элемента, если точки нет, то переменная на элемент не подается. Пример многовходового конъюнктора с входами  показан на рисунке 8 (изображение схемы произведено без учета действующих стандартов. При изображении схемы с учетом ГОСТ необходимо поле входных сигналов располагать с права, а поле выходных сигналов – слева). Упрощенное изображение программируемой логической матрицы реализующую систему функций

показан на рисунке 8 (изображение схемы произведено без учета действующих стандартов. При изображении схемы с учетом ГОСТ необходимо поле входных сигналов располагать с права, а поле выходных сигналов – слева). Упрощенное изображение программируемой логической матрицы реализующую систему функций

,

,

,

,

,

,

показано на рисунке 9. Здесь количество входов m = 4, число термов l = 7, число функций n = 3.

Рисунок 8

Рисунок 9

Как следует из представленного примера интегральная микросхема с программируемой логической матрицей может полностью заменить цифровое устройство, реализующее произвольную логическую функцию. Однако зачастую функциональные возможности таких микросхем полностью не используются. Это проявляется, в частности, при воспроизведении типичных для практики систем логических функций, не имеющих больших пересечений друг с другом по термам. В таких случаях возможность использования выходов любых коньюнкторов (схем И), любыми дизъюнкторами (схем ИЛИ, как это предусмотрено в программируемых логических матрицах) становиться излишним усложнением. Отказ от этой возможности означает отказ от программирования матрицы ИЛИ и приводит к структуре программируемой матричной логики.

В интегральных схемах с программируемыми логическими матрицами выходы элементов И (выходы первой матрицы) жестко распределены между элементами ИЛИ (выходами матрицы ИЛИ) (рисунок 10).

В показанной программируемой матричной логике m входов, n выходов и 4n элементов И, поскольку каждому элементу ИЛИ придается по четыре коньюнктора. Программируемая матричная логика, как и программируемые логические матрицы, воспроизводят дизъюнктивные нормальные формы логических функций, но с более жесткими ограничениями.

В сравнении с программируемыми логическими матрицами схемы программируемой матричной логики имеют меньшую функциональную гибкость, так как в них матрица ИЛИ фиксирована, но их изготовление и использование проще.

Рисунок 10

Преимущества программируемой матричной логики особенно проявляются при проектировании несложных устройств. Продукция класса простых программируемых логических устройств (SPLD), выпускаемая несколькими крупными фирмами, почти исключительно представлена микросхемами программируемой матричной логики (PAL, GAL). Структуры программируемых логических матриц (PLA) типичны для схем формирования управляющих сигналов в машинных циклах микропроцессорных систем и других подобных применений, где они проектируются как часть систем, а не являются автономными микросхемами.

Подготовка задач к решению на программируемой матричной логике имеет много общего с подходом к решению задач на программируемых логических матрицах, но есть и различия. Для задач, решаемых на программируемой матричной логике, важно уменьшить число элементов И в каждом выходном канале, но если для программируемых логических матриц стремятся искать представления функций с наибольшим числом общих термов, то для программируемой матричной логики этого не требуется, поскольку элементы И одного выхода не могут быть использованы другими выходами (то есть для других функций).

Некоторые типы микросхем программируемой матричной логики и их основные параметры приведены в таблице 2.

| Тип микросхемы | Величина задержки, нс | Размер матрицы | Напряжение питания, В |

| GAL16V8D-15LP | 64×32 | ||

| GAL22V10D-25LP | 132×44 | ||

| 16L8-25C | 25 - 30 | 64×32 | 5,5 |

9.5 Воспроизведение скобочных форм логических функций

(на самостоятельное изучение)

Выводы по лекции.

1. Стоимость интегральной схемы зависит от количества выпущенных изделий.

2. Программируемая логика позволяет заменить цифровую схему собранную на дискретных логических элементах

3. Интегральные схемы с программируемыми логическими матрицами имеют больше возможностей по реализации переключательных функций цифровых устройств.

4. Интегральные схемы с программируемой матричной логикой более просты в программировании и производстве.

| <== предыдущая лекция | | | следующая лекция ==> |

| Расшифровка шкал, используемых в таблице | | | Карточки для звуковых схем |

Не нашли, что искали? Воспользуйтесь поиском: