ТОР 5 статей:

Методические подходы к анализу финансового состояния предприятия

Проблема периодизации русской литературы ХХ века. Краткая характеристика второй половины ХХ века

Характеристика шлифовальных кругов и ее маркировка

Служебные части речи. Предлог. Союз. Частицы

КАТЕГОРИИ:

- Археология

- Архитектура

- Астрономия

- Аудит

- Биология

- Ботаника

- Бухгалтерский учёт

- Войное дело

- Генетика

- География

- Геология

- Дизайн

- Искусство

- История

- Кино

- Кулинария

- Культура

- Литература

- Математика

- Медицина

- Металлургия

- Мифология

- Музыка

- Психология

- Религия

- Спорт

- Строительство

- Техника

- Транспорт

- Туризм

- Усадьба

- Физика

- Фотография

- Химия

- Экология

- Электричество

- Электроника

- Энергетика

Транспьютерные топологии

Физические топологии 2D — шина (bus), звезда (star), кольцо (ring), дерево (tree), сетка (mesh)

Классическая МРР - 3D-решетка

Масштабируемость MPP-систем – бесконечна.

Лидер МРР сегодня – кол-во процессоров 200000шт.

Пример: Архитектура TMS320C40

- Концепция, архитектура и характеристики суперкомпьютера Intel Paragon.

MPP (Система с массовым параллелизмом): множество узлов, каждый узел – ОП+ЦП.

Paragon (Intel) – разработка Калифорнийского технологического института, 1992г.

Основан на МП Intel i860 (1989г, RISC).

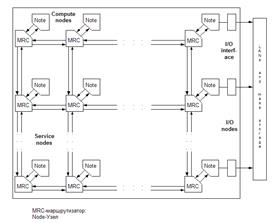

Структура: до 2048 (позже до 4000) i860 были связаны в 2D сетки.

Node – процессные узлы. 3 типа:

1) вычислительные (процессные)

2) сервисные (UNIX-вые возможности для разработки программ).

3) узлы в/в (могут подкл либо к общим ресурсам (дисковым), либо через них реализуется интерфейс с др. сетями).

MRC (маршрутизатор) – набор портов, которые могут связываться между собой и к каждому маршрутизатору может подкл компьютер.

Каждый узел содержал от 1 до 3 МП i860.

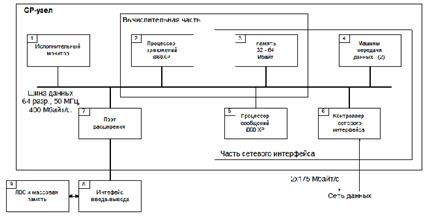

Архитектура Intel Paragon XP/S

Процессный узел Paragon:

Схема процессорного ядра:

1) Исполнительный монитор (позволяет отлаживать, контролировать, записывать работу узла).

2) Процессор приложений

3) ОП (32-64Mb)

4) Машины передачи данных (2 шт): одна на прием, др.на передачу.

5) Процессор сообщений (i860)

6) Контроллер сетевого интерфейса (порты кот-ые выходят на MRC)

7) порт расширения, к кот через интерфейсные карты могли подключатьсяся (8) и (9)

8) Интерфейс в/в

9) К кот подкл: либо ЛВС, либо ЖД.

Выводы разработки Intel Paragon:

1. Для реализации MPP не нужно разрабатывать спец. процессор (проц+дешевая сеть=МРР-решетка 2D, 3D)

2. Нужно брать существующие процессоры, не самые новые, немного устаревшие (дешевле), т.к. важнее кол-во процессоров, а не производительность.

- Иерархия памяти. Архитектурные способы увеличения быстродействия памяти: конвейерная и пакетная обработка, кэширование.

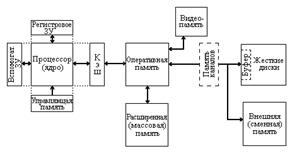

Возможный состав систем памяти:

- В выполняемой программе адреса команд и адреса данных, как правило, находятся в компактной области адресного пространства. Благодаря такой локальности, размещая данные в верхней части иерархии памяти можно существенно улучшить характеристики доступа.

- Пересылка данных с уровня на уровень осуществляется блоками, их величина определяется характеристиками памяти нижнего уровня.

- На пересылку блока уходит меньше времени, чем на пересылку отдельных данных блока.

- При произвольном доступе к данным, время доступа лимитируется самым медленным устройством.

Память с расслоением:

• Наличие в системе множества микросхем памяти позволяет использовать потенциальный параллелизм, заложенный в такой организации. Для этого микросхемы памяти часто объединяются в банки или модули, содержащие фиксированное число слов, причем только к одному из этих слов банка возможно обращение в каждый момент времени.

• Чтобы получить большую скорость доступа, нужно осуществлять одновременный доступ ко многим банкам памяти. Одна из общих методик, используемых для этого, называется расслоением памяти.

• При расслоении банки памяти обычно упорядочиваются так, чтобы N последовательных адресов памяти i, i+1, i+2,..., i+ N-1 приходились на N различных банков. В i-том банке памяти находятся только слова, адреса которых имеют вид kN + i. Можно достичь в N раз большей скорости доступа к памяти в целом, чем у отдельного ее банка, если обеспечить при каждом доступе обращение к данным в каждом из банков. Имеются разные способы реализации таких расслоенных структур.

• Степень или коэффициент расслоения определяют распределение адресов по банкам памяти.

• Такие системы оптимизируют обращения по последовательным адресам памяти, что является характерным при подкачке информации в кэш-память при чтении, а также при записи, в случае использования кэш-памятью механизмов обратного копирования.

• Однако, если требуется доступ к непоследовательно расположенным словам памяти, производительность расслоенной памяти может значительно снижаться.

• Обобщением идеи расслоения памяти является возможность реализации нескольких независимых обращений, когда несколько контроллеров памяти позволяют банкам памяти (или группам расслоенных банков памяти) работать независимо.

Не нашли, что искали? Воспользуйтесь поиском: