ТОР 5 статей:

Методические подходы к анализу финансового состояния предприятия

Проблема периодизации русской литературы ХХ века. Краткая характеристика второй половины ХХ века

Характеристика шлифовальных кругов и ее маркировка

Служебные части речи. Предлог. Союз. Частицы

КАТЕГОРИИ:

- Археология

- Архитектура

- Астрономия

- Аудит

- Биология

- Ботаника

- Бухгалтерский учёт

- Войное дело

- Генетика

- География

- Геология

- Дизайн

- Искусство

- История

- Кино

- Кулинария

- Культура

- Литература

- Математика

- Медицина

- Металлургия

- Мифология

- Музыка

- Психология

- Религия

- Спорт

- Строительство

- Техника

- Транспорт

- Туризм

- Усадьба

- Физика

- Фотография

- Химия

- Экология

- Электричество

- Электроника

- Энергетика

Передача логических сигналов по длинным линиям

Случай, когда сигнал с выхода КМОП-схемы семейства 74НС поступает на вход другой КМОП-схемы, которая включена на конце длинной линии, образованной сигнальным проводом и землей, как показано на рис. 11.9. Сопротивление «открытого» р- или л-канального транзистора на выходе микросхем семейства НСТ равно примерно 100-200 Ом; для простоты примем его равным 150 Ом как при высоком, так и при низком уровне выходного сигнала. Волновое сопротивление типичного соединения в виде дорожки на печатной плате относительно земли находится в пределах 100-150 Ом; давайте для удобства примем его равным 150 Ом, чтобы коэффициент отражения на том конце линии, к которому подключен источник сигнала, был равен 0. Входное сопротивление КМОП-схемы в типичном случае больше 1 МОм, поэтому коэффициент отражения на приемном конце линии можно принять равным +1.

Рис. 11.9. Отражения в линии, по которой передается логический сигнал, изменяющийся от низкого уровня до высокого.

На рисунке представлен случай перехода сигнала с низкого уровня на высокий. Когда уровень сигнала на выходе КМОП-схемы изменяется с низкого на высокий, источник напряжения 5. В оказывается нагруженным последовательно включенными выходным сопротивлением КМОП-схемы, равным 150 Ом, и волновым сопротивлением линии Z0 = 150 Ом, поэтому вдоль линии начинает распространяться волна напряжения с амплитудой 2.5 В. Спустя время Т эта волна достигает входа вентиля U2 на дальнем конце линии и отражается. По прошествии времени 2Т отраженная волна достигает конца, к которому подключен выход логического элемента, и поглощается без отражения, поскольку на этом конце ρ = 0.

Все работает прекрасно в том, что касается вентиля U2 на дальнем конце линии, который «видит» мгновенное изменение напряжения от 0 В до 5 В через время Т после того, как произошло переключение в источнике сигнала. Однако посмотрите на форму сигнала, поступающего на вход другого вентиля U1, расположенного на полпути между источником сигнала и вентилем U2. Как видно из рисунка, на входе вентиля U1 в течение времени Г присутствует сигнал с напряжением только 2.5 В. На входе логического элемента расположенного еще ближе к источнику сигнала, такое напряжение продержится даже дольше. В этом и состоит проблема, поскольку напряжение 2.5 В является как раз пороговым входным напряжением для 5-вольтовых КМОП-схем. Если такое входное напряжение присутствует на входе вентиля U1 достаточно долго, то на его выходе могут возникнуть колебания или установится выходное напряжение, не соответствующее ни одному из логических уровней. Любое соединение, по которому передается логический сигнал, независимо от его физической протяженности, является длинной линией. Однако наше рассмотрение в значительной степени идеализировано. На практике эффекты, возникающие в длинных линиях не вызывают никаких проблем, если время T меньше длительности переходов в логических сигналах и задержек, вносимых логическими элементами. Когда выполнены эти условия, колебания, вызванные отражениями, заканчиваются, как правило, прежде, чем приемники, подключенные к шине, успевают их заметить.

Некоторые неприятности возникают в том случае, когда с высокого уровня на низкий переходит сигнал на выходе быстродействующего элемента. Например, при низком уровне сигнала выходной каскад КМОП-вентиля семейства FCT представляет собой резистор с сопротивлением 10 Ом, включенный между выходом и землей (рис. 11.10). Поэтому коэффициент отражения на передающем конце равен примерно -0.88. В первый момент, когда выходной сигнал переходит на низкий уровень, система выглядит как делитель напряжения, состоящий из резистора с сопротивлением 10 Ом, включенного последовательно с волновым сопротивлением линии, равным 150 Ом. Учитывая, что начальное напряжение на линии равнялось 5В, новое напряжение на входе линии должно стать равным

Следовательно, вдоль линии начнет распространяться волна напряжения с амплитудой (0.31 - 5.0) = -4.69 В. Когда спустя время T эта волна достигает приемного конца линии, происходит отражение с сохранением знака и с той же амплитудой отраженной волны (так как р = 1). Таким образом, напряжение на приемном конце линии теперь равно V2 = 5.0 - 4.69 - 4.69 = -4.38 В, то есть напряжение становится отрицательным! Это явление называется отрицательным выбросом.

возврат на низкий уровень р-

Рис. 11.10. Отражения в линии при изменении передаваемого логического сигнала с высокого уровня на низкий. Когда в момент времени 2Т отраженная волна напряжения с амплитудой —4.69 В возвращается к передающему концу линии, происходит еще одно отражение. На сей раз, поскольку значение р отрицательно, отраженная волна положительна, а ее амплитуда равна -0.88*(-4.69) = + 4.10 В. Теперь напряжение на выходе источника сигнала изменяется на величину, равную сумме амплитуд двух волн: волны, пришедшей со стороны дальнего конца линии, и новой отраженной волны, уходящей в сторону дальнего конца линии; поэтому Vout = 0.31- 4.69 + 4.10 = -0.28 В. В этом месте не возникает никаких проблем. Но когда в момент времени 3^отраженная волна напряжения с амплитудой +4.10 В достигает приемного конца линии, происходит очередное отражение, в результате которого возникает волна той же полярности, и напряжение на входе вентиля U2 становится равным V2 = -4.38 + 4.10 + 4.10 = 3.82 В, то есть мы снова возвращаемся к положительному напряжению!

Согласно рисунку, отражения продолжаются и в дальнейшем, и напряжения на передающем и приемном концах линии асимптотически стремятся к 0 В. Это значение можно было бы предсказать, анализируя поведение схемы по постоянному току. Такой колебательный характер изменения напряжения называется звонам.

Большая амплитуда звона на приемном конце линии может вызвать осложнения, так как в течение интервала времени длительностью 27T напряжение V2 не попадает в диапазон значений, меньших, чем величина порога для сигнала низкого уровня (0.8 В). Таким образом, фактическая задержка передачи сигнала в этой схеме оказывается во много раз больше задержки распространения сигнала по линии. Хуже того, если данный сигнал является тактовым сигналом, то в результате звона появятся дополнительные фронты, приводящие к ошибочному переключению триггеров на приемном конце линии.

Еще раз, рассмотренные нами эффекты, возникающие в длинной линии при передаче логических сигналов, не вызывают никаких проблем в том случае, когда время Т намного меньше длительности переходов в логических сигналах и задержек, вносимых логическими элементами. Кроме того, во входных цепях ТТЛ-схем и многих КМОП-схем имеются демпфирующие диоды. При нормальной работе эти диоды, включенные между каждым из входов и землей, смещены в обратном направлении (см, рис. 3.75). Благодаря наличию этих диодов входное сопротивление вентиля при отрицательных напряжениях становится очень малым, в результате чего отрицательный выброс, возникающий в момент времени Г, оказывается не таким большим по величине и его значение равняется примерно 1 В. Поэтому уменьшается амплитуда отраженной волны, распространяющейся назад к передающему концу линии, что в свою очередь дает меньший выброс в момент времени 3T, не превосходящий 1 В. Кроме того, на входах некоторых схем имеются диоды, подключенные к источнику питания VCC, что ограничивает выбросы напряжения, возникающие тогда, когда сигналы на выходах вентилей с малым выходным сопротивлением переходит с низкого уровня на высокий.

51. Согласованные нагрузки на концах линий передачи логических сигналов

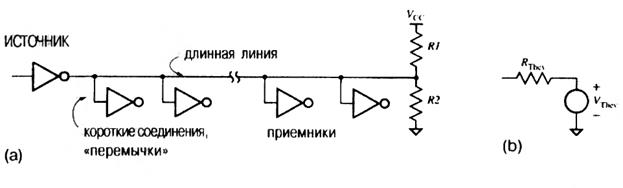

Отражения могут быть устранены при включении в конце длинной линии нагрузки с сопротивлением, равным волновому. Обычно применяются два метода.

Как видно из рис. 11.11(a), оконечная нагрузка состоит из пары резисторов, включенных в конце линии. Согласно теореме Тевенина, эту оконечную нагрузку можно представить в виде эквивалентной схемы, показанной на рис. 11.11(b). При выборе сопротивлений резисторов учитывается несколько факторов:

1. Эквивалентное сопротивление RThev должно равняться волновому сопротивлению линии Z0 или быть близким к нему. Эквивалентное сопротивление равно сопротивлению параллельно соединенных резисторов R1 и R2, то есть (R1 R2)/(R1+R2).

2. Эквивалентное напряжение VThev можно выбрать так, чтобы оптимально удовлетворить требованиям, которые предъявляются к току, втекающему в выходной каскад вентиля, и к току вытекающему из него. В данном случае

|

- Если значения вытекающего и втекающего токов при высоком и низком уровнях сигнала на выходе вентиля, являющегося источником сигнала, передаваемого по линии, равны (как это имеет место в стандартном КМОП-вентиле, не совместимом с ТТЛ-схемами), то значение VThev можно выбрать посредине между VOL и VOH

- С другой стороны, если выходной каскад вентиля таков, что втекающий ток больше вытекающего тока (что имеет место в ТТЛ-схемах и в ТТЛ-совместимых КМОП-схемах), то значение VThev выбирается большим по величине, и тогда, в соответствии с предъявляемыми требованиями, значение вытекающего тока при высоком уровне выходного сигнала будет меньше, а значение втекающего тока при низком уровне выходного сигнала - больше.

3. Для шин с тремя состояниями эквивалентное напряжение VThev можно выбрать так, чтобы оно строго соответствовало тому или иному логическому уровню, когда на шину не подается сигнал ни одним из подключенных к ней источников сигналов. В этом случае особенно важно выбрать значение VThev далеким от порога переключения вентилей, чтобы они не потребляли чрезмерный ток и не переходили в режим колебаний.

4. В конечном счете, сопротивления резисторов выбираются из существующих номинальных значений (например, 150, 220, 270, 330, 390, 470 Ом).

«Стандартная» оконечная нагрузка в устройствах с ТТЛ-схемами выглядит следующим образом: RI = 220 Ом, R2 = 330 Ом, что дает RThev = 132 Ом и К = 3.0 В. При низком уровне выходного сигнала источник сигнала должен допускать втекание тока, равного (3.0 В)/(132 Ом) = 22.7 мА, а высокий уровень выходного сигнала надежно поддерживается даже в том случае, когда вытекающий ток источника сигнала равен 0.

При согласованной нагрузке в конце длинной линии отражений не будет или они будут небольшими. Нижний резистор оконечной нагрузки - это та часть на» грузки, которая всегда потребляет мощность по постоянному току, и от источника сигнала требуются относительно большие токи. Согласование со стороны источника иногда называемое последовательным согласованием решает эти проблемы.

Как показано на рис. 11.12, между длинной линией и источником сигнала, физически рядом с ним, последовательно включается резистор с сопротивлением (Z0-Rd), где Rd - характерное значение выходного сопротивления источника сигнала. Форма сигналов в линии при таком согласовании приведена на рис. 11.13. При переходе напряжения на выходе вентиля от значения VCC к 0 (или наоборот) источник сигнала нагружен сопротивлением 2Z0, получающимся в результате сложения сопротивления добавочного резистора и сопротивления самой линии. Из всего перепада напряжения одна половина падает на выходном сопротивлении вентиля и добавочном резисторе, а другая приложена к входу линии. Таким образом, спустя время T равное времени распространения сигнала по линии, вентиль U2 на дальнем конце линии видит изменение напряжения VCC/2. В связи с тем, что коэффициент отражения равен 1, этот перепад напряжения тотчас же отражается назад к источнику сигнала, что приводит к повышению напряжения на входе U2 до величины Vсс Отраженная волна достигает источника сигнала и поглощается в согласованной нагрузке с сопротивлением Z0, в результате чего новые отражения в линии не возникают. Согласование со стороны источника сигнала хорошо работает в том случае, когда выходные сопротивления источника сигнала при низком и высоком уровнях на его выходе можно считать практически равными (как, например, у КМОП-схем). В типичных схемах при волновых сопротивлениях линий порядка 50—100 Ом применяют добавочные резисторы с сопротивлениями 15-40 Ом.

Согласование со стороны источника сигнала нежелательно в том случае, когда какие-либо вентили, такие, например, как вентиль U1 на рис. 11.13, размещаются где-то посередине длинной линии. При изменении сигнала начальный перепад на входах «средних» вентилей, составляет только Vсс/2; полный перепад возникает только тогда, когда подойдет отражение от дальнего конца. Плохо, если такое состояние длится очень долго, поскольку напряжение Vсс/2 может оказаться близким к порогу переключения вентиля.

5. Простейшая схема защиты от дребезга

6. Шинный фиксатор уровня

7. Биполярные последовательностные ПЛУ

8. Последовательностные устройства типа GAL

8_8. Последовательные устройства типа GAL

9. Временные характеристики ПЛУ

10. Самое распространенное в мире применение регистров сдвига

11. Последовательно-параллельное преобразование

12. последовательно-параллельное преобразование

13. Итерационные и последовательностные схемы

14. Методология синхронного проектирования

15. Структура синхронной системы

16. Разброс задержек тактового сигнала

17. Стробирование тактового сигнала

18. Асинхронные входы

19. Сбой в работе синхронизирующего устройства и метастабильность

20. Сбой в работе синхронизирующего устройства

21.Время выхода из метастабильности

22.Разработка надежного синхронизирующего устройства

23.Анализ времени пребывания в состоянии метастабильности

24. Более совершенные синхронизирующие устройства

25. Другие схемы синхронизирующих устройств

26. Триггеры с защитой от метастабильности

27. Синхронизация при высокоскоростной передаче данных

28.Интегральные схемы типа CPLD

29. Семейство ИС XC9500 фирмы Xilinx

30. Архитектура функционального блока

31. Архитектура блока ввода/вывода

32. Переключающая матрица

33. Интегральные схемы типа FPGA

34. Семейство ИС типа FPGA ХС4000 фирмы Xilinx

35. Перестраиваемый логический блок

36. Блок ввода/вывода

37. Программируемые соединения

38. Средства автоматизированного проектирования

39. Языки описания схем

40 Ввод схемы

41 Временные диаграммы и временные параметры

42. Анализ схемы и моделирование

43. Разработка печатной платы

44. Проектирование, предусматривающее тестируемость

45. Тестирование

46. Тестер с игольчатыми контактами и внутрисхемное тестирование

47. Методы сканирования

48. Оценка надежности цифровой системы

49. Основы теории длинных линий

50. Передача логических сигналов по длинным линиям

51. Согласованные нагрузки на концах линий передачи логических сигналов

Не нашли, что искали? Воспользуйтесь поиском: