ТОР 5 статей:

Методические подходы к анализу финансового состояния предприятия

Проблема периодизации русской литературы ХХ века. Краткая характеристика второй половины ХХ века

Характеристика шлифовальных кругов и ее маркировка

Служебные части речи. Предлог. Союз. Частицы

КАТЕГОРИИ:

- Археология

- Архитектура

- Астрономия

- Аудит

- Биология

- Ботаника

- Бухгалтерский учёт

- Войное дело

- Генетика

- География

- Геология

- Дизайн

- Искусство

- История

- Кино

- Кулинария

- Культура

- Литература

- Математика

- Медицина

- Металлургия

- Мифология

- Музыка

- Психология

- Религия

- Спорт

- Строительство

- Техника

- Транспорт

- Туризм

- Усадьба

- Физика

- Фотография

- Химия

- Экология

- Электричество

- Электроника

- Энергетика

Логика на комплементарных МОП транзисторах (КМДП)

Микросхемы на комплементарных парах транзисторов строятся на основе МОП транзисторов с n- и p-каналами. В этих схемах один и тот же потенциал открывает транзистор с n-каналом и закрывает транзистор с p-каналом.

Простейший логический КМОП элемент – это инвертор. Его схема приведена на рисунке 3.15. При формировании логической единицы открыт верхний транзистор, а нижний закрыт. В результате ток через микросхему не протекает. При формировании логического нуля открыт нижний транзистор, а верхний закрыт. И в этом случае ток через микросхему не протекает.

Рисунок 3.15 – Принципиальная схема инвертора, выполненного на комплементарных МОП транзисторах

На схеме, приведённой на рисунке 3.15, для упрощения понимания принципов работы микросхемы, не показаны защитные и «паразитные» диоды. Особенностью микросхем на комплементарных МОП транзисторах является то, что эти микросхемы в статическом режиме практически не потребляют ток.

Потребление тока происходит только в момент переключения микросхемы из единичного состояния в нулевое и наоборот. Этим током перезаряжается паразитная ёмкость нагрузки цифровой микросхемы.

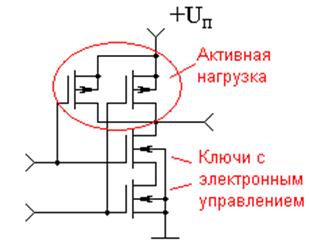

Схема логического элемента "И-НЕ" на КМОП микросхемах практически совпадает с эквивалентной схемой логического элемента "И" на ключах с электронным управлением, которую мы рассматривали ранее. Отличие заключается в том, что нагрузка подключается не к общему проводу схемы, а к источнику питания. Это приводит к инверсии сигнала на выходе логического элемента. Принципиальная схема элемента "2И-НЕ", выполненного на комплементарных МОП транзисторах приведена на рисунке 3.16.

В этой схеме можно было бы применить в верхнем плече обыкновенный резистор, однако при формировании напряжения низкого уровня схема постоянно потребляла бы ток. Вместо этого, в приведённой на рисунке 3.16 схеме, в качестве нагрузки используются p-МОП транзисторы. Эти транзисторы образуют активную нагрузку. Если на выходе логического элемента требуется сформировать высокий потенциал, то нагрузочные p‑МОП транзисторы открываются, а если низкий – то закрываются.

Рисунок 3.16 – Принципиальная схема элемента "2И-НЕ", выполненного на комплементарных МОП транзисторах

В приведённой на рисунке 3.16 схеме ток от источника питания на выход микросхемы будет поступать через один из транзисторов нагрузки, если хотя бы на одном из входов (или на обоих сразу) будет присутствовать низкий потенциал (уровень логического нуля). Если же на обоих входах будет присутствовать уровень логической единицы, то оба p-МОП транзистора будут закрыты, ток от источника питания поступать не будет, и на выходе микросхемы сформируется низкий потенциал. В этой схеме, так же как и в схеме инвертора, приведённой на рисунке 3.15, если хотя бы один из транзисторов верхнего плеча будет открыт, то соответствующий транзистор нижнего плеча будет тоже закрыт. Поэтому в статическом состоянии ток от источника питания логическим элементом потребляться не будет.

Условно-графическое изображение такого логического элемента показано на рисунке 3.5, а его таблица истинности приведена в таблице 3.1. В таблице 3.1 входы обозначены как x1 и x2, а выход – F.

Логический элемент "ИЛИ-НЕ", выполненный на КМОП транзисторах, представляет собой параллельное соединение ключей с электронным управлением. Отличие от схемы "2ИЛИ", рассмотренной ранее, заключается в том, что нагрузка подключается не к общему проводу схемы, а к источнику питания. Это приводит к инверсии выходного сигнала. Вместо резистора в качестве нагрузки используются p-МОП транзисторы. Принципиальная схема элемента "2ИЛИ-НЕ", выполненного на комплементарных МОП транзисторах приведена на рисунке 3.17.

Рисунок 3.17 – Принципиальная схема элемента "2ИЛИ-НЕ", выполненного на комплементарных МОП транзисторах

В схеме логического элемента "2ИЛИ-НЕ" в качестве нагрузки используются последовательно включенные p-МОП транзисторы. В ней ток от источника питания будет поступать на выход микросхемы, только если все транзисторы в верхнем плече будут открыты, т.е. если сразу на всех входах будет присутствовать низкий потенциал (уровень логического нуля). Если же хотя бы на одном из входов будет присутствовать уровень логической единицы, то верхнее плечо будет закрыто, и ток от источника питания поступать на выход микросхемы не будет.

Таблица истинности, реализуемая схемой, приведенной на рисунке 3.17, соответствует таблице 3.2, а условно-графическое обозначение этого элемента приведено на рисунке 3.7.

В настоящее время именно КМОП микросхемы получили наибольшее развитие. Причём наблюдается постоянная тенденция к снижению напряжения питания этих микросхем. Первые серии КМОП микросхем, такие как К1561 (зарубежный аналог C4000В) обладали достаточно широким диапазоном изменения напряжения питания (3..18В). При понижении напряжения питания у конкретной КМОП микросхемы понижается её предельная частота работы и наоборот (на этом явлении основан так называемый разгон современных центральных процессоров персональных компьютеров). В дальнейшем, по мере совершенствования технологии производства, появились улучшенные КМОП микросхемы с лучшими частотными свойствами. Однако для этого потребовались транзисторы с меньшими линейными размерами, что привело к меньшим допустимым напряжениям питания.

Не нашли, что искали? Воспользуйтесь поиском: