ТОР 5 статей:

Методические подходы к анализу финансового состояния предприятия

Проблема периодизации русской литературы ХХ века. Краткая характеристика второй половины ХХ века

Характеристика шлифовальных кругов и ее маркировка

Служебные части речи. Предлог. Союз. Частицы

КАТЕГОРИИ:

- Археология

- Архитектура

- Астрономия

- Аудит

- Биология

- Ботаника

- Бухгалтерский учёт

- Войное дело

- Генетика

- География

- Геология

- Дизайн

- Искусство

- История

- Кино

- Кулинария

- Культура

- Литература

- Математика

- Медицина

- Металлургия

- Мифология

- Музыка

- Психология

- Религия

- Спорт

- Строительство

- Техника

- Транспорт

- Туризм

- Усадьба

- Физика

- Фотография

- Химия

- Экология

- Электричество

- Электроника

- Энергетика

Функциональная схема.

Функционально установка состоит из следующих узлов (схема представлена на рис. 4):

· арифметико - логического устройства (АЛУ);

· восьми одноразрядных сумматоров (SM);

· регистров операндов А, В, С;

· коммутаторов каналов 4 на 1;

· запоминающего устройства микрокоманд (DS);

· счетчика адреса микрокоманд;

· триггера D-типа;

· генератора синхроимпульсов и счетчика циклов;

· блока управления в аппаратном режиме работы;

· блока управления в микропрограммном режиме работы.

Арифметико - логическое устройство и сумматоры размещены в съемном блоке. При подключении к установке съемного блока стороной “аппаратное управление” работают схемы сумматоров. При подключении стороной “микропрограммное управление” - работает АЛУ.

Все управление работой составляющих частей установки осуществляются блоком кассет, где расположены: генератор синхроимпульсов, счетчик циклов и блоки управления в аппаратном и микропрограммном режимах работы. При этом в аппаратном режиме работы включаются ячейки 1, 2, 3, 4, а в микропрограммном режиме - ячейки 1, 2, 5, 6.

Все прочие устройства (регистры операндов, коммутатор каналов, запоминающее устройство, счетчик адреса, триггер D-типа) размещены на печатных платах лицевой панели.

Арифметико-логическое устройство (АЛУ) – расположено в съемном блоке. АЛУ построено на основе двух схем К155ИП3 (электрическая схема рис. 5), представляющих собой четырехразрядное логическое устройство, которое может выполнять 16 логических и 16 арифметических операций.

Тип выполняемой операции (логическая или арифметическая) определяется уровнем сигнала на входе “М”, сама операция задается комбинацией сигналов на входах S0, S1, S2, S3, а также состоянием входа С0 - входящий перенос в младшую группу К155ИП3. Коды полей микрокоманд для выполняемых на установке операций приведены в приложении 1.

При выполнении арифметических операций поразрядный перенос вырабатывается по принципу одновременного параллельного формирования переноса в четырех разрядах. Для формирования переноса из младшей четырехразрядной группы в старшую используется схема К155ИП4. Работа АЛУ осуществляется в микропрограммном режиме, где состояние управляющих входов определяется соответствующими полями микрокоманды.

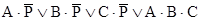

Одноразрядный сумматор К155ИМ1 реализует функции суммы S и переноса Р в соответствии с формулами:

S =

где А, В - операнды, подаваемые на вход сумматора, С - входящий перенос.

Распространение переноса в восьмиразрядном сумматоре последовательное. Работа сумматора осуществляется в аппаратном режиме управления.

Регистры операндов расположены на лицевой панели. Регистры служат для записи исходной информации, промежуточных и конечных результатов выполнения операции.

Регистр операнда “А” является регистром хранения информации. Он построен на микросхемах К155ТМ8, содержащих в корпусе четыре D-триггера, соединенных между собой по входу синхронизации и входу установки нуля. На выходе регистра установлена логика на микросхемах К155ЛР1, позволяющая в зависимости от выполняемой операции (в аппаратном режиме работы) использовать прямое или инверсное значение операнда “А”, что определяется подачей сигнала V RGA.

Регистры операндов “В” и “С” построены на микросхеме К155ИР13, которая может работать в следующих режимах:

| V1 | V2 | Режим работы регистра |

| запись информации параллельная с входов D. | ||

| сдвиг информации в сторону младших разрядов. | ||

| сдвиг информации в сторону старших разрядов. | ||

| хранение информации. |

Выбор режима определяется наличием сигналов на управляющих входах V1, V2 и тактового сигнала С.

Все регистры имеют встроенную индикацию на светодиодах.

Расположение информации в регистрах и структура операндов для каждой из операций приведены в приложении 3.

Коммутатор каналов 4х1 конструктивно расположен на одной ячейке с регистром операнда “С”. Коммутатор каналов собран на микросхемах К155КП2.

В зависимости от кода операции коммутатор каналов производит выбор одного из четырех источников информации для записи ее в регистр С. Выбор конкретного информационного канала происходит при соответствующей комбинации на адресных входах А1, А2 и наличии стробирующего сигнала на входе С.

Запоминающее устройство микрокоманд выполнено на микросхемах К155РУ2, представляющих собой ОЗУ со схемами управления и полной дешифрацией адреса. Емкость ЗУ - 16 восьмиразрядных слов. ЗУ работает в микропрограммном режиме и служит для записи и хранения микропрограммы одной операции.

Для хранения одной микрокоманды используется три восьмиразрядных слова (24 бита). Максимальная длина микропрограммы - 5 микрокоманд.

ЗУ имеет встроенную индикацию на выходе для проверки записываемой информации (индикация работает только при записи).

Счетчик адреса микрокоманд построен на универсальном счетчике К155ИЕ7, который работает в трех режимах:

установка адреса по входам Д0...Д3 при присутствии импульса по входу V.

счет адреса по входу “+1”.

обнуление счетчика по входу R.

Триггер D-типа (обозначение на лицевой панели - ТТ) конструктивно размещен на одной печатной плате со счетчиком адреса. Служит для запоминания:

· переполнения разрядной сетки при операциях сложения, вычитания, умножения модулей;

· знака операнда “В” при операции умножения в дополнительных кодах;

· дешифрированного состояния 0 и 1 разрядов операнда “В” при операции ускоренного умножения.

Генератор синхроимпульсов построен на двух линиях задержки Лз1 и Лз2, одна из которых - Лз2 - определяет длительность синхроимпульсов - 0.4 мкс, а другая Лз1 - интервал между двумя сериями импульсов - 0.5 мкс.

Генератор вырабатывает 4 серии синхроимпульсов СИ1...СИ4, которые выводятся на конкретные гнезда съемного блока. Временные диаграммы приведены на рис. 6

Также в генераторе вырабатываются 4 серии рабочих тактовых импульсов, 3 серии рабочих управляющих импульсов и импульс счета циклов длительностью 100 нс.

В ячейке 1 генератора синхроимпульсов расположен генератор одиночного импульса, с помощью которого запускается цикл выполнения операции в одиночном режиме, а также запускается и останавливается запись информации в ЗУ в режиме “Запись”.

Счетчик циклов (ячейка 2) расположен в блоке кассет. Счетчик, построенный на микросхеме К155ИЕ5, служит для определения конца цикла выполняемой операции в обоих режимах работы установки.

На ячейке 2 расположены схемы, определяющие условия порядка выполнения действий при операции ускоренного умножения на два разряда и операции деления.

Блок управления в аппаратном режиме работы выполнен на двух ячейках 3 и 4.

Ячейка 3 - формирователь тактовых сигналов - включает в себя дешифратор кода операции, триггер, управляющий занесением исходных операндов и выполнением операции и логические схемы, вырабатывающие, в зависимости от кода операции и некоторых дополнительных условий, последовательность тактовых сигналов, необходимых для выполнения заданной операции.

Ячейка 4 - формирователь управляющих сигналов, содержит только логические схемы, вырабатывающие сигналы управления в соответствии с заданной операцией для схем, расположенных на панели.

Блок управления в микропрограммном режиме включает в себя ячейки 5 и 6.

Ячейка 5 - управление счетчиком адреса. В данной схеме дешифрируется код операции на микросхеме К155ИД3 и в зависимости от условий, приходящих от счетчика циклов, от признаков, устанавливаемых набором на лицевой панели и полей S0...S3 микрокоманды (Управляющих входов АЛУ) вырабатывается адрес микрокоманды, которая будет выполняться, а также формируются управляющие сигналы “+1 СТ Адр”,“V СТ Адр” и “сброс СТ Адр”. Сброс счетчика адреса вырабатывается после выполнения всей операции. Таким образом, микропрограмма для выполнения любой из операций записывается в соответствии с приложением 5, начиная с нулевого цикла.

Ячейка 6 - регистр микрокоманды. Регистр построен на шести микросхемах К155ИР1. Выборка одной микрокоманды из ОЗУ осуществляется по трем тактовым импульсам, по восемь разрядов за такт. Каждая микрокоманда занимает в ОЗУ три ячейки памяти.

Не нашли, что искали? Воспользуйтесь поиском: