ТОР 5 статей:

Методические подходы к анализу финансового состояния предприятия

Проблема периодизации русской литературы ХХ века. Краткая характеристика второй половины ХХ века

Характеристика шлифовальных кругов и ее маркировка

Служебные части речи. Предлог. Союз. Частицы

КАТЕГОРИИ:

- Археология

- Архитектура

- Астрономия

- Аудит

- Биология

- Ботаника

- Бухгалтерский учёт

- Войное дело

- Генетика

- География

- Геология

- Дизайн

- Искусство

- История

- Кино

- Кулинария

- Культура

- Литература

- Математика

- Медицина

- Металлургия

- Мифология

- Музыка

- Психология

- Религия

- Спорт

- Строительство

- Техника

- Транспорт

- Туризм

- Усадьба

- Физика

- Фотография

- Химия

- Экология

- Электричество

- Электроника

- Энергетика

ТРИ ПРОЦЕССОРНЫХ ЯДРА HC08

При современном программировании приложений на языке Си, изучать архитектурные особенности процессорного ядра, как правило, не обязательно. Поэтому дана сравнительная характеристика трёх модификаций процессорного ядра НС08. На её основе можно сделать осознанный выбор модели МК для конкретного приложения.

Все три рассматриваемых процессорных ядра: НС08, HCS08 и RS08, -выполнены на основе CISC-архитектуры. Программно-логическая модель центрального процессора НС08 (см. рис. 298) содержит пять регистров, которые не являются частью объединённого адресного пространства, и, следовательно, для обращения к ним должны быть использованы специальные команды. Это 8-разрядный аккумулятор АСС, 16-разрядный индексный регистр НХ (Н - старший байт, X - младший байт), 16-разрядные программный счётчик PC и указатель стека SP, 8-разрядный регистр признаков CCR. Последний содержит пять флагов, информирующих о состояния операнда в аккумуляторе: переноса (С), нулевого результата (Z), отрицательного результата (N), переполнения (V),дополнительного переноса

Рис. 298. Программно-логическая модель центрального процессора НС08.

(Н), а также бит глобальной маски прерывания (I). Размещение триггера запрета всех прерываний центрального процессора I в регистре признаков является традиционным для всех МК компании Freescale Semiconductor.

Программный счётчик, указатель стека и регистр НХ позволяют линейно адресовать все 64 Кб памяти, что обусловливает две особенности системы команд:

- во-первых, подавляющее число действий исполняется над операндами, которые могут быть расположены в любом адресном пространстве из 64 Кб;

- во-вторых, МК с процессорным ядром НС08 могут одинаково успешно исполнять программы как из ПЗУ, так и из ОЗУ. Последнее существенно упрощает построение модуля внутрисхемной отладки.

Система команд ядра НС08 включает 90 инструкций языка Ассемблер, в том числе команды целочисленного беззнакового умножения восьмиразрядных операндов (время выполнения операции составляет 5 циклов или 625 нс) и целочисленного беззнакового деления 16: 8 (время выполнения операции - 7 циклов или 875 нс). Операция сложения или вычитания однобайтовой константы выполняется за 250 нс (2 цикла).

Центральный процессор НС08 поддерживает 12 способов адресации, имеет двухадресные команды, которые позволяют выполнять пересылки данных между двумя ячейками памяти или регистрами специальных функций, минуя регистры центрального процессора. Процессор оснащён большим набором команд ветвления. Кроме переходов по традиционным условиям С, Z, N, Н, реализованы переходы по комбинациям флагов С и Z для сравнения операндов в прямом коде без знака, а также по комбинациям флагов С, Z, и V для сравнения операндов в дополнительном коде со знаком. Общее число инструкций ветвления ассемблера НС08 равно 40. Процессорное ядро НС08 реализует векторные прерывания, а также имеет специальную команду программного прерывания.

Программно-логическая модель и система команд процессорного ядра HCS08 полностью идентична ядру НС08. В чём же отличия?

Во-первых, использован новый технологический процесс, что позволило повысить частоту внутренней шины до 20 МГц при напряжении питания 3,6 В.

Во-вторых, процессорное ядро HCS08 работает в диапазоне напряжений питания от 1,8 до 3,6 В, т.е. ориентировано на работу в устройствах с автономным питанием.

В-третьих, процессорное ядро HCS08 имеет расширенный набор режимов энергосбережения, что полезно в автономных приборах.

В-четвертых, процессорное ядро HCS08 имеет более совершенный модуль отладки, реализующий режим BDM (BDM - Background Debug Mode, т.е. фоновый режим отладки). В отличие от модуля отладки, реализованного в НС08, новый модуль отладки позволяет часть функций выполнять без останова исполнения прикладной программы. Кроме того, для перевода МК в режим отладки используется всего одна линия, что для маловыводных МК очень важно. В рассматриваемых МК на основе процессорного ядра НС08 с интерфейсом отладки MON08 иногда до половины выводов должны быть использованы в режиме отладки. Поэтому приходится коммутировать выводы, а лишние разъёмы нежелательны в малогабаритных приложениях.

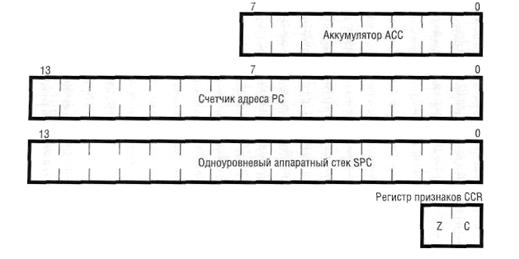

Обратимся теперь к ядру RS08. При его разработке преследовалась цель предельно минимизировать аппаратные средства 8-разрядного процессорного ядра, ориентированного на очень простые приложения с объёмом программного кода в несколько килобайт. Программно-логическая модель центрального процессора RS08 представлена на рисунке 2. Она содержит 8-разрядный аккумулятор АСС, 14-разрядный счётчик команд PC, 14-разрядный регистр SPC и двухразрядный регистр признаков CCR.

Уменьшенная разрядность программного счётчика PC свидетельствует о том, что максимальный объём программного кода для этого процессорного ядра составляет 16 Кб. Наличие всего двух флагов условий (переполнения С и нулевого результата Z) в регистре состояния CCR определяет ориентацию этого процессорного ядра на выполнение, в основном, логических операций и на очень простые вычисления, которые не предполагают использования представления чисел со знаком. И, как следствие, в системе команд отсутствуют инструкции умножения и деления. Существенно сократилось и число команд ветвления - в предыдущих версиях процессорного ядра HC08/HCS08 их было 40, в версии RS08 осталось всего 11.

Существенные изменения претерпела модель памяти и система адресации. Процессорное ядро RS08 использует страничную систему адресации, при которой линейно адресуются лишь ячейки памяти с адресами 0x00 - OxFF. Старшие 64 адреса (ОхСО - OxFF) рассматриваются как окно для обращения к одной из 252 страниц постоянной памяти объёмом 64 байта каждая. Для выбора номера страницы предназначен новый регистр управления PAGESEL. Три страницы памяти с младшими адресами (ОxОО - OxBF) адресуются линейно. В этом адресном пространстве располагаются ОЗУ МК и регистры управления периферией.

Число способов адресации операндов сократилось с 12 в предыдущих

версиях процессорного ядра до 7 в версии RS08. Изменение модели памяти и способов адресации имело целью сократить число байтов кодов команд, что позволило повысить плотность управляющего кода. Теперь двухбайтовое представление операнда используют только команды безусловного перехода jmp adr и вызова подпрограмм jsr adr. Остальные команды, в том числе арифметические и логические, имеют только двухбайтовый или даже однобайтовый формат. Это достигается введением двух способов прямой адресации, которые ранее были несвойственны микроконтроллерам.

Freescale Semiconductor - это прямая адресация типа Tiny, при которой возможно обращение только к операндам, расположенным по адресам ОxОО - OxOF, и прямая адресация типа Short, для которой доступны ячейки памяти с адресами ОхОО - OxIF.

Следует обратить внимание на интересное архитектурное решение, которое позволило эмулировать индексный регистр косвенной адресации X, унаследованный от предыдущих версий процессорного ядра (см. рис. 298), и связанные с ним способы индексной адресации со смещением и автоинкрементированием после выборки операнда. Теперь регистр косвенной адресации X располагается в оперативной памяти МК. При обращении с использованием прямой адресации к другому регистру оперативной памяти D[X] происходит выборка операнда, расположенного по адресу, значение которого содержится в X (см. рис. 30). Таким образом, разработчики процессорного ядра RS08 сумели сохранить в системе команд такие способы адресации, как индексная (косвенная по регистру X), индексная со смещением в 8 или I6 бит, индексная со смещением и автоматическим увеличением на 1 содержимого X после выборки операнда. В самом центральном процессоре таких способов адресации нет, поэтому площадь кристалла велика, а для программиста эти способы адресации доступны.

Существенные изменения претерпела подсистема вызова подпрограмм и подсистема прерываний. В процессорном ядре RS08 отсутствует указатель стека SP (см. рис. 29), вместо которого появился регистр одноуровневого аппаратного стека SPC (Shadow PC). В этот регистр загружается адрес возврата при вызове подпрограммы или при переходе на подпрограмму прерывания. Организация многоуровневого вызова подпрограмм возможна только с применением специальных программных конструкций. Для этого предусмотрены команды передачи содержимого регистра SPC в оперативную память и обратно.

Рис. 29. Программно-логическая модель центрального процессора НС08.

Подсистема прерываний процессорного ядра RS08 перестала быть векторной. Микроконтроллеры типа MC9RS08KA1/KA2 имеют пять источников запросов на прерывания: модуль таймера MTIM, внешние запросы на входах портов KBI, аналоговый компаратор АСМР, модуль меток реального времени RTI и запрос от модуля слежения за пониженным напряжением питания LVD. События запросов отображаются в специальном регистре, который должен быть опрошен программой для определения источника запроса на прерывание. Очень важно, что подсистема прерывания в МК MC9RS08KA1/KA2 предназначена только для вывода этих МК из режимов пониженного энергопотребления типа ожидания (Wait) или останова (Stop). При работе МК в активном режиме, т.е. в процессе исполнения программы, подсистема прерывания запросы фиксирует, но не изменяет ход выполнения программы. Флаги запросов должны программно опрашиваться, и при необходимости выполняется ветвление программы управления.

Что же получилось в итоге столь существенных изменений? Процессорное ядро RS08 сохранило хорошую систему команд, которая была свойственна ядру HC08/HCS08. По существу не стало только команд умножения и деления. Но при отсутствии в МК встроенного АЦП и наличии упрощённого таймера, который не предполагает измерения временных интервалов, эти команды требуются редко.Сохранилось множество способов

Рис. 30. Эмуляция индексной адресации в процессорном ядре RS08.

адресации, хотя все способы, связанные с регистром X, теперь эмулируются на уровне программы Ассемблера или компилятора с языка Си.

Существенно изменилась логика организации работы МК в реальном времени. Отсутствует возможность прерываний от внешних и внутренних источников в ходе выполнения программы, но все события фиксируются, запоминаются и могут быть опрошены программно, что для небыстрых приложений вполне допустимо.

Очень важно, что процессорное ядро RS08 унаследовало от ядра HCS08 режим фоновой внутрисхемной отладки BDM. Для данного класса МК он удобен по двум причинам. Во-первых, можно следить за изменением ресурсов МК в режиме отладки без останова выполнения программы, поскольку приложения достаточно простые и медленные. Во-вторых, вход в режим отладки и взаимодействие с МК в процессе отладки происходит по единственному выводу, что делает возможным использование отладки в системе даже при корпусе МК с шестью выводами.

Не нашли, что искали? Воспользуйтесь поиском: