ТОР 5 статей:

Методические подходы к анализу финансового состояния предприятия

Проблема периодизации русской литературы ХХ века. Краткая характеристика второй половины ХХ века

Характеристика шлифовальных кругов и ее маркировка

Служебные части речи. Предлог. Союз. Частицы

КАТЕГОРИИ:

- Археология

- Архитектура

- Астрономия

- Аудит

- Биология

- Ботаника

- Бухгалтерский учёт

- Войное дело

- Генетика

- География

- Геология

- Дизайн

- Искусство

- История

- Кино

- Кулинария

- Культура

- Литература

- Математика

- Медицина

- Металлургия

- Мифология

- Музыка

- Психология

- Религия

- Спорт

- Строительство

- Техника

- Транспорт

- Туризм

- Усадьба

- Физика

- Фотография

- Химия

- Экология

- Электричество

- Электроника

- Энергетика

БЕРІЛГЕН ЕКІЛІК ЖҮЙЕДЕГІ А МЕН В САНДАРЫН КӨБЕЙТУ АМАЛЫ

А= 0101 – код 8421

В= 1011 – код 8421

А –A4А3 А2 А1

В –B4В3 В2 В1

А3А2А1

B4В3 В2 В1

(А3В1)(А2В1)(А1В1)

+ (А3В2)(А2В2)(А1В2)

(А3В3)(А2В3)(А1В3)

(A3B4)(A2B4)(A1B4)

S6 S5 S4 S3 S2 S1

Ондық сандарды сақтаған кезде ондық сандардың әр бір саны екілік формада беріледі, мұндай сандардың ретін екілік- кодпен жазылған ондық жүйе деп аталады. Сандық техникада n дәрежелі сандарды сақтау үшін n элементі бар тізбектелген қондырғыларды қолдануға болады.

Ондық санды екілік формада көрсету үшін, санды екіге тізбектей бөлу керек. Мысалы 16 санын тізбектей екіге бөлсек келесідей сандар комбинациясы болады: 10000. Екілік санды кері ондыққа айналдыру үшін, әр дәрежені тізбектей көбейту қажет.

2 ШИФРЛАУШЫНЫ СИНТЕЗДЕУ(Қ1)

Шифрлеуіш (кодер) – деп, "N-нен 1" коданы екілік кодқа түрлендіру үшін пайдаланатын, комбинациалық типті функционалдық түйінді айтады.

Шифрлеуіштің кірісіне тізбекті түрде ондық сандар мәндері меншіктеледі. Шифрлеуіштің кірістерінің біріне белсенді (активті) логикалық сигналды бергенде, оның шығысында активтелінген кірістің нөміріне (яғни ондық санға) сәйкес екілік код түзіледі (пайда болады).

2 п кірісі және п шығысы бар шифрлеуіш толық деп аталады. Ал егер шифрлеуіштің кірісінің саны 2 п -нен кіші болса, онда ол толық емес деп аталады.

Шифрлаушылар сандық қондырғыларда ақпаратты енгізу құрылғыларында және оның басқада блоктарында телебасқару телесигнализация жүйелерінде кеңінен қолданылады. Шифрлаушы пассифтік радиокомпонеттерден және логикалық элементтердің түрінде орындалады, интегралды түрде орындалған шифрлаушылар кең таралған.

Бізге осы курстық жобада коды 8421 шифрлық коды НЕМЕСЕ-ЕМЕС базисіндегі шифрлаушы құруымыз керек, басқалай айтқанда негізгі логикалық элементтер, дизьюнктор бұл екілік сандардың логикалық қосылуын орындайды.

Біріншіден біз ақиқат кестесін 8421 кодына сәйкес толтырамыз (2.1 кесте) Содан соң дизьюкция арқылы бейнеленген ақиқат кестесі негізіндешифрлаушының шығыс функциясын жазамыз, осыдан кейін шифрлаушының схемасын саламыз, НЕМЕСЕ- ЕМЕС интегралды логикалық элементе істелінген.

| Ондық сан У | Х4 | Х3 | Х2 | Х1 |

2.1 кесте 8421 кодтағы шифрлаушының ақиқат кестесі.

Осы ақиқат кестесі арқылы НЕМЕСЕ-ЕМЕС базисінде логикалық теңдеуді жазамыз.

x1 =  ;

;

x2 =  ;

;

x3 =  ;

;

x4 =  ;

;

Берілген тапсырмаға сәйкес алынған функцияның нәтижсін НЕМЕСЕ–ЕМЕС базисіне Де-Морган заңын қолдану арқылы келтіру қажет.

x1 =  ;

;

x2 =  ;

;

x3 =  ;

;

x4 =  ;

;

НЕМЕСЕ-ЕМЕС интегралды логикалық элементте құралған шифрлаушының схемасын сызамыз, K155ЛA1 схемасында жасалған.

| & |

2 6

К155ЛА1 микросхемасындағы НЕМЕСЕ – ЕМЕС логикалық элементі

К155ЛН1 микросхемасындағы ЕМЕС логикалық элементі

3 ЕКІЛІК – ОНДЫҚ САНАҚШЫНЫҢ МИКРОСХЕМАСЫН СИНТЕЗДЕУ (Қ2)

Бұл курстық жобада екінші көбейткіш В санын ондық- екілік санақшы арқылы 8421 кодына әкелінеді.

Санашы - импульстердің әрбір сәйкесті ауытқымасында кұрамындағы санды бірге өзгертіп отыратын құрылғы. Құрамындағы санның өзертілу бағытына байланысты тура, теріс және әмбебап санақшылар болады. Санақшылар Т-триггерлердің негізінде құрылады.

Ксч –сандық автоматтың ішкі күйлерінің саны.

Мүмкін Ксч =2k, мұнда k – бүтін сан болса, онда санақшы екілік деп аталады.

Мүмкін Ксч = 10k-онда ондық санақшы.

Ен қарапайым санақшы– бұл триггер. Оның Ксч =2, өйткені ол екі күйде де бола алады.

Триггерлерді қосу мезетіне байланысты санақшылар синхронды және асинхронды болып бөлінеді. Асинхронды қосылу мезетінде триггерлердің бір күйден екінші күйге ауысуы кезекпен жүреді, ал синхронды болғанда триггерлар бірдей бір мезетте ауысады.

Cанақшылар қосатын және шегеретін болады.

Қосатын және шегеретін санақшылармен қатар реверстік есептеуіштер қолданулар табады. (+, -).

Бұл бөлімде біз санақшыны синтездейміз. Кез келген санақшыны синтездеу үшін, кез келген сандық қондырғыныкіндей ақиқат кестесі маңызды болып келеді. Осы жағдайда- бұл 8421 кодындағы кесте (кесте 2.1). Санақшыны құрастыру үшін Т-триггерлары, D-триггерлары және JK-триггерларын қолдануға болады, біз бұдан JK-триггеррін таңдаймыз. Біз JK - триггерды таңдаған себебіміз, бұл триггер арқылы J және K кірістерін тізбектей қосып Т-триггерын құрастыра аламыз.

Санақшының күйлерінің жинақ (кесте 3.2) кестесін құрастыру үшін JK-триггеррінің ауысу (кесте 3.1) кестесін пайдаланып толтырамын.

Кесте 3.1 JK триггерінің ауысу кестесі.

Ақиқат кестесінде триггерлердің бір қалыптан екінші қалыпқа тізбектей ауысуы сарапталады, бірінші х1 бағанынан бастап санақшының ауысу кестесімен сәйкестендіреді, санақшы күйінің жинақ кестесінің J1, K1 бағанына, одан соң х2, х3, х4 бағандарына сәйкестендіріп J2, K2, J3, K3, J4, K4 бағандарын толтырып санақшының күйлерінің толық жинақ кестесін аламын.

| J1 | K1 | J2 | K2 | J3 | K3 | J4 | K4 | |

| - | ||||||||

| - | - | |||||||

| - | - | |||||||

| - | - | - | ||||||

| - | - | |||||||

| - | - | - | ||||||

| - | - | - | ||||||

| - | - | - | - | |||||

| - | - | |||||||

| - | - | - | ||||||

| - | - | - | ||||||

| - | - | - | - | |||||

| - | - | - | ||||||

| - | - | - | - | |||||

| - | - | - | - | |||||

| - | - | - | - |

Кесте3.2 Cанақшының күйінің жинақ кестесі.

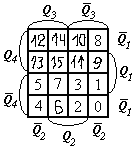

Вейча картасын пайдаланып әрі қарай санақшыны құрау үшін логикалық теңдеудің функцияларын алу қажет. Вейча картасын толтыруға қолайлы болуы үшін өзінің толтыру тәртібі бар. (3.3 кесте)

Кесте 3.3 Вейча диаграммасын толтыру тәртібі және де шығыс триггерінің параметрлеріне сәйкес жазылуы.

Вейча картасы қолданатын минимизациялау әдісі көрнекі және қарапайым минимизациялау түрі болып табылады. Және бұл жағдайда АЛФ бейнелеудің графикалық әдісі қолданылады. Вейча картасы 2n квадратты тікбұрышты бейнелейді, мұндағы n – графикалық түрде бейнелеуге қажетті бульдік функцияның айнымалылар саны. n – жұп кезінде, тікбұрыштың әрбір жағы ұяшықтан тұрады, ал n – тақ кезінде тікбұрыштың бір жағы  ұяшықтан, ал басқа жағы

ұяшықтан, ал басқа жағы  ұяшықтан тұратды. n аргументке тәуелді АЛФ-ң кез келген екі диаграммасы n+1-аргументке тәуелді АЛФ диаграммасын қолданады.

ұяшықтан тұратды. n аргументке тәуелді АЛФ-ң кез келген екі диаграммасы n+1-аргументке тәуелді АЛФ диаграммасын қолданады.

Диаграммадағы әрбір ұяшыққа сәйкес элементарлы конъюнкция (аргументтер жиынтығы) қойылады, және де бұл жағдайда көршілес конъюнкциялар сәйкес келеді. Екі шеткі қарама қарсы қатарлар мен бағаналардағы ұяшықтар да көршілес конъюнкциялар болып саналады (диаграмма торда орналасқан деп елестетуге болады).

Санақшы күйінің кестесі арқылы толтырылған Вейча карталары 3.1 суретте сәйкестендіріліп көрсетілген. Вейча диаграммасындағы логикалық бір (1) орналасқан торларды 2, 4, 8, 16 топтастырып біріктіру жолымен санақшыны құрайтын JK – триггерлерінің кірістері мен шығыстарын жалғауға қажетті логикалық функцияның теңдеуін алып, сол арқылы санақшыны синтездеймін

.

J1 K1

| - | - | - | - |

| - | - | - | - |

| - | - | - | - |

| - | - | - | - |

J2 K2

| - | - | ||

| - | - | ||

| - | - | ||

| - | - |

| - | - | ||

| - | - | ||

J3 K3

| - | - | ||

| - | - | ||

| - | - | ||

| - | - |

| - | |||

| - | |||

J4 K4

| - | - | - | - |

| - | - | - | - |

| - | |||

Сурет 3.1 Санақшы күйінің кестесіне сәйкестендіріліп толтырылған

Вейча диаграммасы.

Нәтижесінде мынадай логикалық функциялардың теңдеуін аламын:

J1=  ; K1=

; K1=

J2=  ; K2=

; K2=  ;

;

J3=  ; K3 =

; K3 =

J4=  ; K4=

; K4=

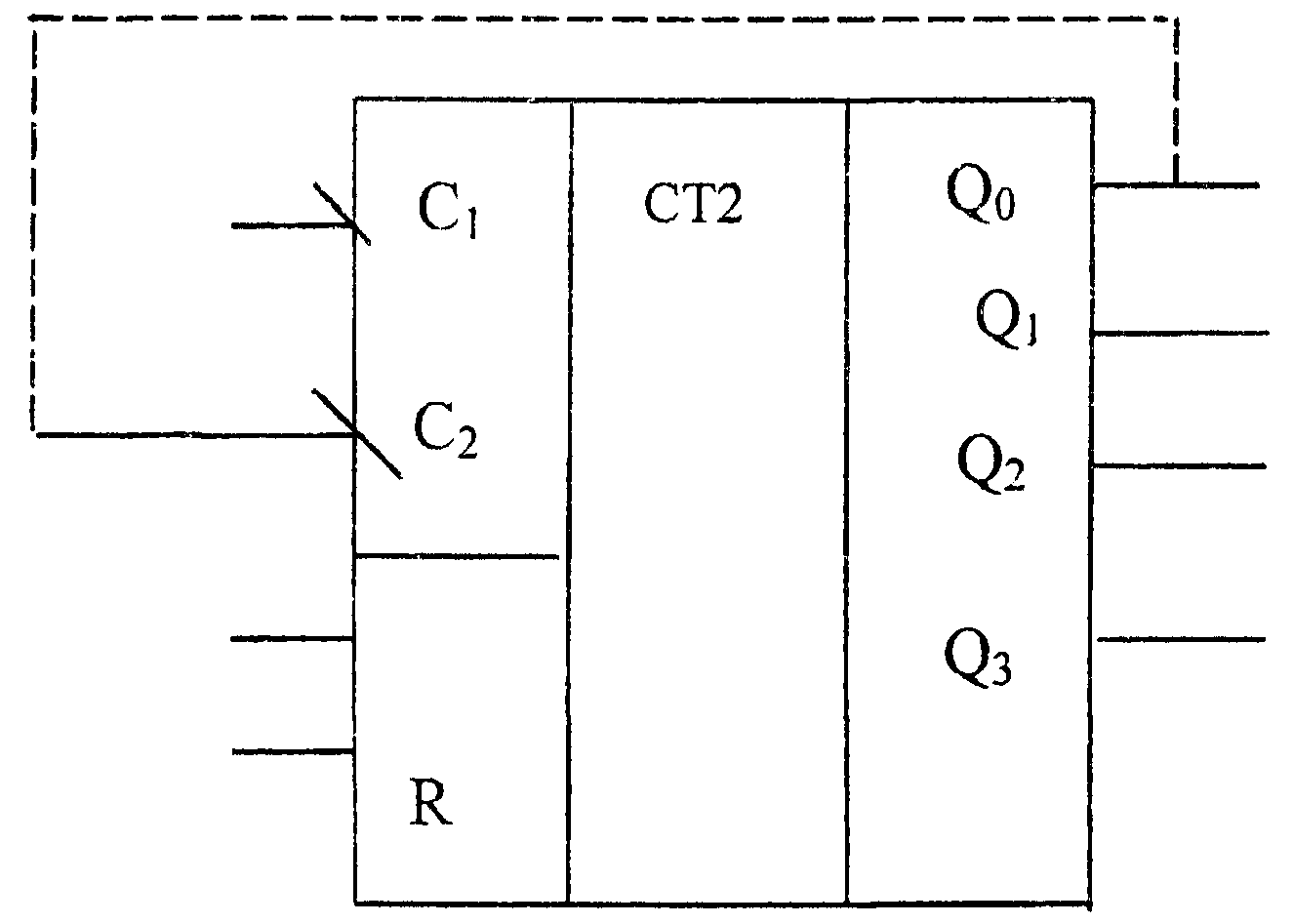

(3) суретте төрт JK – триггері арқылы синтезделген санақшының сұлбасы берілген, ал (3.3) суретте осы санақшының кері байланыс арқылы шартты графикалық белгіленуі көрсетілген және К155ИЕ5 микросхемасында құрастырылған.

К155ИЕ5 микросхемасы асинхронды екілік санақшы болып келеді. Ол Т- триггерлерден тұрады және 0 келтіретін екі R кірісі бар.

Сурет 3.3 Құрастырылған санақшының К155ИЕ5 микросхемасы мен

шартты графикалық белгіленуі.

4 АРАЛАС ЛОГИКАЛЫҚ СХЕМАЛАРЫ (Қ3, Қ4, Қ5, Қ6)

Комбинациялық логикалық сұлбалар (КЛС) – коньюктор элементі арқылы құрастырылады және көбейту амалын орындайды. Шығыстағы әрбір мән, дәл сол уақыт мезетінде кірісіне келіп түскен дабылдардың көбейтілген мәніне сәйкес анықталады.

Бұл бөлімде екілік сандарды көбейту операциясын жүзеге асыру қажет, ол үшін – коньюнктор немесе логикалық «2ЖӘНЕ» элементі пайдаланылады.

5 суретте комбинациялық логикалық сұлба көрсетілген, онда әрбір коньюнктордың кірісі мен шығысындағы мәндер көрсетілген, яғни бұл құрылғы сандарды көбейтуге арналған.

Тапсырмаға байланысты Қ3, Қ4, Қ5, Қ6 комбинациялық логикалық сұлбасының микросхемасын таңдауымыз қажет.

А мен В екі оң таңбалы сандарды көбейткен кезде келесі жартылай көбейтінді шығады:

А4В1, А3В1, А2В1 , А1В1 – 1- жартылай көбейтінді.

А4В2, А3В2, А2В2 , А1В2 – 2- жартылай көбейтінді

А4В3, А3В3, А2В3 , А1В3 – 3- жартылай көбейтінді

А4В4, А3В4, А2В4, А1В4 - 4- жартылай көбейтінді

А және В сандарын кіші разрядтан бастап көбейту үшін К555ЛИ1 микросхемасын қолданамыз

А= 0101 – код 8421 А –A4 А3 А2 А1

В= 1011 – код 8421 В –B4 В3 В2 В1

А4 А3 А2А1 101

B4 В3 В2 В1 1011

(А3В1)(А2В1)(А1В1) 101

+ (А3В2)(А2В2)(А1В2) 101

(А3В3)(А2В3)(А1В3) 000

(A3B4)(A2B4)(A1B4) 101

S6 S5 S4 S3 S2 S1 110111

5 ЫҒЫСТЫРУШЫ РЕГИСТРЫН ТАҢДАУ (Қ7, Қ8, Қ9)

Регистр – бұл сандық қондырғы, көп разрядты сандарды сақтауға арналған.

Регистр – триггерлердің жинағынан тұрады, әр қайссы белгілі бір сандарды сақтауға арналған. Сонымен қоса n – разрядты санды сақтау үшін қажет регистр, n- триггердан тұратын. Регистрлар келесі міндеттер атқарады: регистрда сақталған санды, яғни белгілі бір сандық разрядты солға және онға ығыстыруды, санды паралельді пішіннен тізбекті пішінге және керісінше айналдыруы орындайды.

Регистрға енгізілетін санның пішініне қарай регистрлар екі топқа бөлінеді: тізбекті және параллель.

Паралелльді регистрде барлық разрядтағы сандар кіріске бір мезетте кіреді.

Тізбекті регистрға, кіріс сандары кіші разрядтан бастап жеке жеке кіреді.

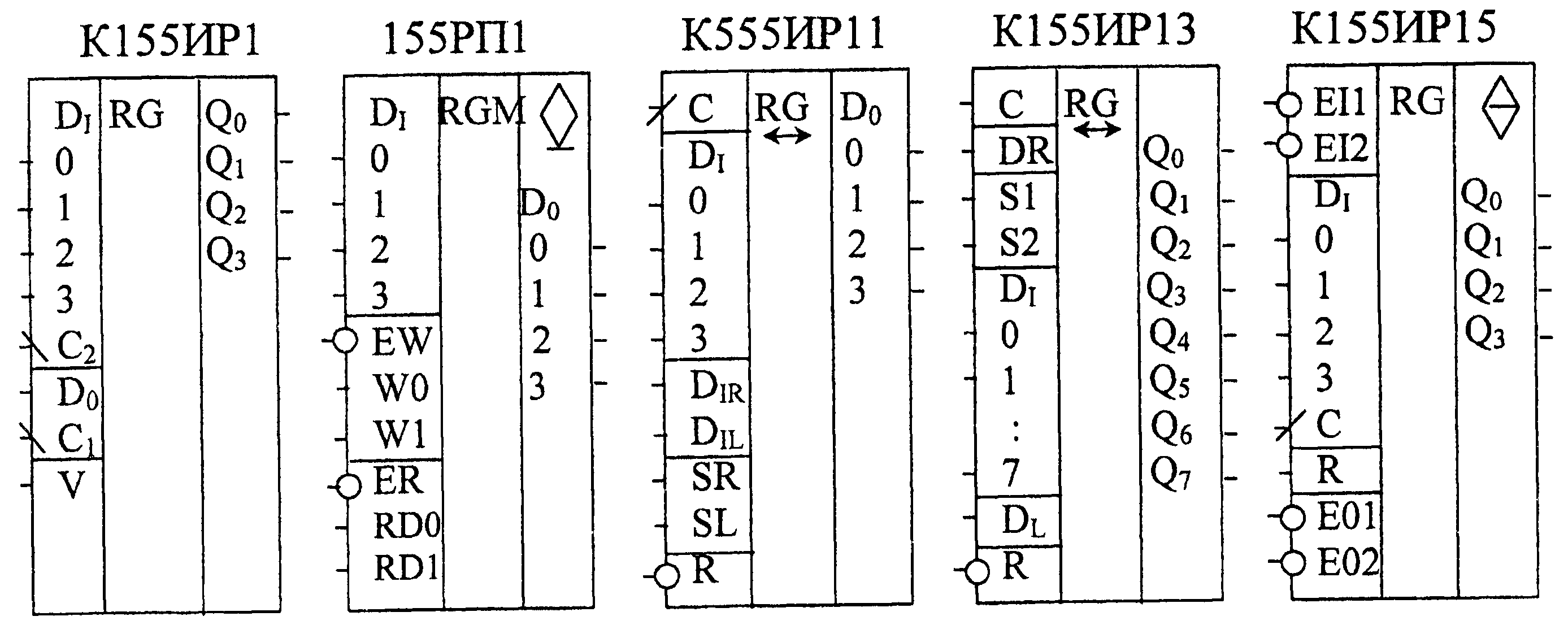

5.1 суретте паралелльді регистрдің микросхемасы берілген К555ИР11, уақытша сандарды тіркеп, ығыстыруға арналған саны бір данадан қолданылады.

К555ИР11 микросхемасы – бұл мәліметті сақтайтын регистр, төрт разрядты, яғни төрт D-триггерден тұрады. Триггердегі жазу режимі С кіріске синхронды тактілі импульстің түсуіне байланысты.

R кіріске логикалық нөл түскен кезде триггерлерде жою режимі болады.

К555И11 микросұлбалары әмбебап ығыстыру тіркегіші болып табылады. Олар мәліметті оңға қарай да және солға қарай да ығыстыра алады. Тіркегіштің SR, SL екі басқарушы кірістерің көмегімен төрт мүмкін болатын жұмыс режимінің бірі таңдап алынады:

-SR, SL кернеуді төмен деңгейде бергенде тіркегіштегі мәліметтер ығыспайды, тіркегіш сақтау режімінде болады.

-SR=1, SL=0 болып оңға ығыстыру режімі кезінде, тізбекті кіріс DiR түсетін мәліметтер оңға қарай бір орынға әрбір тактылы импульстің оң мәнді айырымы бойынша ығысады.

-SR=0, SL=1- мәліметтерді ығыстыру режімі, бірінен кейін бірі келетін мәліметтер DIL, солға қарай әрбір тактылы импульстің оң мәнді айырымы бойынша ығысады.

-SR=SL=1 - мәліметтерді параллель жазу режімі кезінде тактылы импульс кірісі шебі бойынша D0-D3 параллель кірісінен жазылады.

Тіркегіштің жұмыс режимін тактылы импульстердің өте жоғары деңгейіне өзгертуге болады.

Тіркегіштің асинхронды R- кірісі бар: оған төменгі деңгейлі кернеуді бергенде мәліметтерді жою (тіркегішті тазалау) жүреді, D і 0¸D і 3 шығыстарында төменгі деңгейдегі кернеу орналасады.

Микросұлбалар пайдаланатын I ток күшінің мәні К555ИР11 үшін І =23мА, К155ИР11 І =63мА, К531ИР11 І =135мА. Максимал тактылы жиілік К155ИР11 үшін ¦=25 МГц, К531ИР11 үшін f=70 MГц. К555ИР11 микросүлбесі үш күйдегі шығысы бар төрт разрядты ығыстырушы тіркегіші болып табылады.

Сурет 5.1 Параллельді регистр К555ИР11

СУММАТОРДЫ

ТАҢДАУ (Қ10, Қ11, Қ12)

Әрі қарай шыққын жартылай көбейтінділерді жинастыру, яғни жолдарды өзара қосу керек, бұл операцияны сумматор құрылғысы жасайды.

Сумматор – екілік санау жүйесіндегі сандарды бір бірімен қосу амалын жүргізеді.

6.1 суретте сумматордың жұмыс істеу принципінің ақиқат кестесі.

| Кіріс | Шығыс | |||

| Қосылғыштар | Ауысу | Қосынды | Ауысу | |

| Аi | Вi | Рi | Si | Рi+1 |

Төрт разрядты сумматордың төрт қос кірісі және төрт шығыс арнасы болады. S- қосу амалының нәтижесі шығатын, ал Р- қосындының сәйкесті разрядына симаған, жоғарғы разрядқа көшіруге дайындалған цифр орналасатын арна.

Сумматорда есте сақтау қабілеті жоқ, яғни кірістегі сигнал өзгерсе шығыстағы мәліметтер өзгеріп отырады. Күйлер кестесіне байланысты сумматор жұмыс істейді.

Сумматорда көп разрядты сандардың жинақталуы каскад бойынша қосылады, яғни тасымалдағы разрядты Р шығысын келесі Р0 кірісімен жалғастыру үшін. Екілік сандарды азайту үшін сумматор қолданылады. Алулар бұл операцияда санның азайғышының кодының алмастыруы жинақтау операциясы жолымен қосымшаға алмастырады, P асыра толтыруын дәреже есепке алмайды. Бiрлiктiң қосымшасы сөздiң кiшi дәрежесiнiң сумматорының тасымалдауы кiрісіне 1-шi сигналдың беруiмен жүзеге асырылады

Жинақталатын, яғни қосылатын сандардан кірістерге А коды беріледі (А1 –кіші разряд, А4 – үлкен разряд), В кірістеріне – екінші санның коды (В1 – кіші разряд, В4 – улкен разряд). Р0 –келесі микросхемадан тасымалдау. Соманың коды S-тың шығуларында қалыптасады, ал тасымалдау Р– шығысында.

Біздің тапсырмамызға сәйкес, үш төрт разрядты сумматор төрт жартылай көбейтінді жолдарын біртіндеп жинақтап, қосу операциясын орындайды (сурет-4)

Сурет 6.2 К155ИМ3 микросхемадағы сумматордың шартты графикалық белгіленуі.

7 ЕКІЛІК САНДАРДЫ ПАРАЛЕЛЬ ПІШІННЕН ТІЗБЕКТЕГІ ТҮРЛЕНДІРЕТІН РЕГИСТР (Қ13)

Бұдан әрi, байланыстағы мәндер арқылы сандық көбейткіштен толық қорытынды нәтижені алу үшiн сумматордан алынған шығымды параллель пішіннен сызық- тізбекті пішінге түрлендiретін, оңға ығыстырғыш регистрдың микросхемасын таңдаймын.

7.2 суретте корсетілген К555ИР9микросүлбесі сегізразрядты реверсивті әмбебап тіркегіш болып табылады. Бұл микросүлбеде жалғау санын азайту мақсатында - кристалдан шығатын сегіз жалғау  мәліметтерді параллель жазу кезінде кірістер болып қызмет атқарады, ал параллель санау кезінде шығыстар болып қызмет атқарады. Тіркегіш динамикалы тактылы инверсті С-кірістері бар D-триггер негізінде жасалған. і -разрядының шығысы мультиплексор арқылы (і +1) және (і -1) разрядтарының D-кірістерімен жалғанған.

мәліметтерді параллель жазу кезінде кірістер болып қызмет атқарады, ал параллель санау кезінде шығыстар болып қызмет атқарады. Тіркегіш динамикалы тактылы инверсті С-кірістері бар D-триггер негізінде жасалған. і -разрядының шығысы мультиплексор арқылы (і +1) және (і -1) разрядтарының D-кірістерімен жалғанған.

Разряд аралық бұл байланыстан басқа әрбір триггердің шығысы үшінші Z-күйі бар бүйірлік күшейткіш кірісімен жалғанады (7.1-сурет). Бүйірлік күшейткіштер күйін басқару  және SR,SL кірістері арқылы іске асырылады. Кернеудің төмен деңгейінде екі кірісінде "шығуға рұқсат"

және SR,SL кірістері арқылы іске асырылады. Кернеудің төмен деңгейінде екі кірісінде "шығуға рұқсат"  және SR, SL кез келгенде кірісінің біреуінде (немесе екеуіңде) тіркегіштің тандау режімінде барлық сегіз бүйірлік күшейткіш жұмыс істейтін күйде тұрады.

және SR, SL кез келгенде кірісінің біреуінде (немесе екеуіңде) тіркегіштің тандау режімінде барлық сегіз бүйірлік күшейткіш жұмыс істейтін күйде тұрады.

Барлық  жалғаулары микросүлбенің шығыстары болып табылады, оларда тіркегіште сақгалған ақпарат бар (санау режімінде). Жоғары деңгейлі кернеу

жалғаулары микросүлбенің шығыстары болып табылады, оларда тіркегіште сақгалған ақпарат бар (санау режімінде). Жоғары деңгейлі кернеу  кірісінің кез келген біреуінде (немесе екеуінде) болған кезде барлық бүйірлік күшейткіштер ажыратылған Z - күйінде тұрады және

кірісінің кез келген біреуінде (немесе екеуінде) болған кезде барлық бүйірлік күшейткіштер ажыратылған Z - күйінде тұрады және  жалғаулары ақпараттық кіріс болып табылады.

жалғаулары ақпараттық кіріс болып табылады.

7.1 - сурет КР531ИР24 микросүлбелерінің D1/0 жалғауларын ұйымдастыру

Мәліметтерді тізбекті таңбамен жазу үшін микросүлбеде - D0 (оңға ығыстыру), D7 (солға ығыстыру) кірістері бар және мәліметтерді санау үшін соларға сәйкес Q0, Q7 шығыстары бар.

Тіркегіштің жұмыс режімі SR, SL кірістеріндегі сигналдармен беріледі:

SR =1, SL=0 оңға ығысу,

SR=0, SL =1 солға ығысу,

SR= SL =1 параллель жазу,

SR=SL=0 сақтау.

R-асинхронды алып тастау кірісіндегі кернеудің төменгі деңгейі тіркегішті нөлдік күйге әкеледі. Тіркегіш микросүлбесі 60 мА ток күшін пайдаланады, 35 МГц жоғары тактылы максимал жиілікте жұмыс істейді. Тіркегіштің жүктемелік қабілеті үлкен, жұмыс кезіндегі тоғы І 0 =30 мА-ден артық болады.

Сурет 7.1 Параллелді – тізбекті реверсивті ығыстырғыш регистр К555ИР9

8 ОҢ ТАҢБАЛЫ ЦИФРЛЫҚ

Не нашли, что искали? Воспользуйтесь поиском: