ТОР 5 статей:

Методические подходы к анализу финансового состояния предприятия

Проблема периодизации русской литературы ХХ века. Краткая характеристика второй половины ХХ века

Характеристика шлифовальных кругов и ее маркировка

Служебные части речи. Предлог. Союз. Частицы

КАТЕГОРИИ:

- Археология

- Архитектура

- Астрономия

- Аудит

- Биология

- Ботаника

- Бухгалтерский учёт

- Войное дело

- Генетика

- География

- Геология

- Дизайн

- Искусство

- История

- Кино

- Кулинария

- Культура

- Литература

- Математика

- Медицина

- Металлургия

- Мифология

- Музыка

- Психология

- Религия

- Спорт

- Строительство

- Техника

- Транспорт

- Туризм

- Усадьба

- Физика

- Фотография

- Химия

- Экология

- Электричество

- Электроника

- Энергетика

Синхронизация при высокоскоростной передаче данных

Широко распространенной проблемой, возникающей в компьютерных системах, является синхронизация переноса данных, поступающих по внешним линиям, с внутренним тактовым сигналом компьютера.

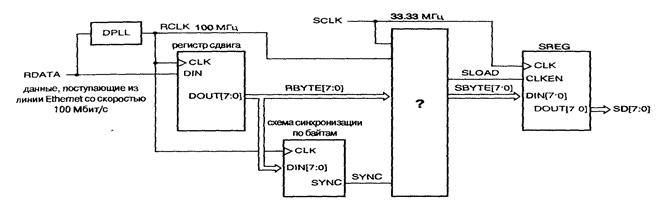

Эта проблема схематически представлена на рис. 1. Последовательные данные RDATA, представленные в коде NRZ, принимаются по линии Ethernet со скоростью 100Мбит/с. Цифровая схема ФАПЧ (Digital Phase-Locked Loop, DPLL) извлекает 100-мегагерцный тактовый сигнал RCLK из потока данных, поступающих со скоростью 100 Мбит/с, и позволяет заталкивать данные побитно в 8-разрядный регистр сдвига. В то же самое время схема синхронизации по байтам ищет в принимаемом потоке данных последовательность битов специального вида, которой отмечаются границы между байтами. Обнаруживая одну из них, схема синхронизации по байтам выдает сигнал SYNC и поступает так на каждом восьмом такте сигнала RCLK; таким образом, сигнал SYNC возникает всякий раз, когда регистр сдвига содержит выровненный по границам 8-битовый байт принимаемых данных. В остальной части системы тактирование осуществляется тактовым сигналом SCLK с частотой 33.33 МГц. Нам необходимо переносить каждый выровненный по границам байт RBYTE[7:0] в регистр SREG, находящийся в той части системы, которая работает с тактовым сигналом SCLK.

На рис. 2 приведены несколько временных диаграмм. Сразу видно, что сигнал выравнивания байтов по границам SYNC имеет активный уровень только в течение 10 нс в пределах байта. Нет никакой надежды, что удастся каждый раз привязывать этот сигнал к системному тактовому сигналу SCLK, период которого, равный 30 нс, много больше.

Стратегия, которой следуют практически всегда в ситуации подобного рода, состоит в том, что сначала выровненные по границам данные заносят в регистр хранения HREG по тактовому сигналу RCLK из принимаемого потока данных. Это дает нам значительно больше времени, в данном случае - 80 нс, чтобы разобраться с принятым байтом. Таким образом, блок, помеченный вопросительным знаком "?" на рис. 1, можно заменить схемой, показанной на рис. 3, состоящей из регистра HREG и узла, названного "SCTRL". Функция этого узла заключается в вырабатывании сигнала SLOAD в течение точно одного периода системного тактового сигнала SCLK, равного 30 нс, так, чтобы сигналы на выходах регистра HREG на этом интервале оставались постоянными и тем самым было удовлетворено требование неизменности сигнала в течение времени установления и времени удержания регистра SREG, переключающегося по сигналу SCLK.

Стратегия, которой следуют практически всегда в ситуации подобного рода, состоит в том, что сначала выровненные по границам данные заносят в регистр хранения HREG по тактовому сигналу RCLK из принимаемого потока данных. Это дает нам значительно больше времени, в данном случае - 80 нс, чтобы разобраться с принятым байтом. Таким образом, блок, помеченный вопросительным знаком "?" на рис. 1, можно заменить схемой, показанной на рис. 3, состоящей из регистра HREG и узла, названного "SCTRL". Функция этого узла заключается в вырабатывании сигнала SLOAD в течение точно одного периода системного тактового сигнала SCLK, равного 30 нс, так, чтобы сигналы на выходах регистра HREG на этом интервале оставались постоянными и тем самым было удовлетворено требование неизменности сигнала в течение времени установления и времени удержания регистра SREG, переключающегося по сигналу SCLK.

Рис 3.

Рис 3.

Правила, которые могут помочь при конструировании синхронизирующих устройств:

· Минимизируйте число подсистем, работающих с различными тактовыми сигналами.

· Четко определите границы между всеми тактовыми сигналам и и в явном виде поместите на этих границах синхронизирующие устройства.

· Обеспечьте для каждого синхронизирующего устройства достаточное время выхода из метастабильности, чтобы сбои синхронизирующих устройств были редкими и происходили с много меньшей вероятностью, чем возникновение неисправности в других местах.

· Проанализируйте работу синхронизирующего устройства при различных возможных сдвигах сигналов во времени, в том числе при более быстрых и более медленных тактовых сигналах, которые могут подаваться на схему при моделировании или при модернизации системы.

· Осуществите моделирование работы системы в широком диапазоне возможных временных соотношений между сигналами.

Не нашли, что искали? Воспользуйтесь поиском: