ТОР 5 статей:

Методические подходы к анализу финансового состояния предприятия

Проблема периодизации русской литературы ХХ века. Краткая характеристика второй половины ХХ века

Характеристика шлифовальных кругов и ее маркировка

Служебные части речи. Предлог. Союз. Частицы

КАТЕГОРИИ:

- Археология

- Архитектура

- Астрономия

- Аудит

- Биология

- Ботаника

- Бухгалтерский учёт

- Войное дело

- Генетика

- География

- Геология

- Дизайн

- Искусство

- История

- Кино

- Кулинария

- Культура

- Литература

- Математика

- Медицина

- Металлургия

- Мифология

- Музыка

- Психология

- Религия

- Спорт

- Строительство

- Техника

- Транспорт

- Туризм

- Усадьба

- Физика

- Фотография

- Химия

- Экология

- Электричество

- Электроника

- Энергетика

Суперскалярні мікропроцесори з RISC-архиітектурою

RISC-архітектура є основою сучасних робочих станцій і серверів. Елементи архітектури із спрощеною системою команд застосовували в суперкомп'ютерах Cray. У 1980 р. були розроблені машини RISC-I і RISC-II. Їх головними ідеями було відділення повільної пам'яті від швидкодіючих регістрів і використання регістрових вікон. Роком пізніше було опубліковано описання машини MIPS, основним аспектом якої була ефективна реалізація конвеєрної обробки за допомогою детального планування компілятором його завантаження.

Остаточне поняття архітектури RISC в сучасному вигляді сформувалося на базі проектів трьох комп'ютерів - RISC, 801 фірми IBM і MIPS.

Загалом RISC-архітектура має такі риси:

· порівняно невеликий (скорочений) набір команд, які більше всього застосовуються в прикладних програмах;

· трьохоперандний формат команд з довжиною операндів 32 або 64 розряди;

· невелике число способів адресації;

· великий регістровий файл (16, 32,64 і більш за регістри);

· апаратна реалізація простих команд за один машинний такт;

· звернення до пам'яті за допомогою спеціальних команд завантаження-запам'ятовування, що обробляють групу регістрів;

· широке використання регістрових вікон при перемиканні завдань;

· суперскалярність – за один машинний такт виконуються дві й більше команд;

· передбачення переходів;

· наявність засобів підтримки багатопроцесорності.

У цілому структура RISC -процесорів містить:

· два і більше виконавчих пристроїв, зокрема з плаваючою комою;

· роздільні Кеші команд і даних;

· блок прогнозування переходів;

· інтерфейс з 64-розрядною зовнішньою шиною даних.

Розробкою і промисловим випуском RISC -процесорів займається ряд відомих фірм. Вони надають своїм виробам власні назви архітектури, наприклад:

· POWER – фірма IBM, Power РС – фірми Motorola, Apple і IBM;

· Alpha – фірма DEC;

· MIPS – фірма MIPS Technology та інші.

Розглянемо особливості побудови і функціонування процесорів з архітектурою POWER.

Архітектура POWER

Архітектура POWER – це розвиток ідей, які було закладено в основу процесора IBM 801 у напрямку реалізації суперскалярної обробки, скорочення довжини конвеєра і часу виконання команд та пріоритетної орієнтації на ефективне виконання операцій з плаваючою комою.

Архітектура POWER у багатьох відношеннях є традиційною RISC -архітектурою, яка має фіксовану довжину команд, прості способи адресації, операції регістр-регістр і трьохоперандний формат команд. Проте архітектура POWER має додаткові властивості, що відрізняють її від іншої архітектури:

· набір команд заснований на ідеї суперскалярної обробки, де в процесорі команди розподіляються між трьома незалежними виконавчими пристроями: переходів, з фіксованою і плаваючою комою, при цьому команди одночасно поступають і закінчуються в цих трьох пристроях.

· архітектура POWER розширена декількома "змішаними" командами: групового завантаження і запам'ятовування регістрів, автоінкрементної адресації, операцій з полями бітів тощо;

· архітектура переходів у POWER організована за принципом попереднього перегляду умовних переходів;

· архітектура POWER визначає розширені властивості регістра умов (прапорців), для цього вводиться спеціальний біт в коді операції в кожній команді для модифікації регістра умов, а також використовуються вісім регістрів прапорців, що розширює кількість бітів умов.

Після першої реалізації архітектури POWER (1990 р.) з'явилися процесори P0WER2 і POWER2+.

Багатокристальний набір POWER2 складається з восьми напівзамовних мікросхем:

· блок кеш-пам'яті команд- 32 Кбайт;

· пристрій цілочисельної арифметики АЛП з двома конвеєрами і двома блоками регістрів; у кожному блоці є 32 регістри завдовжки 32 біти; передбачено забезпечення цілочисельних і логічних операцій і всіх звернень до пам'яті;

· пристрій операцій з плаваючою комою FPU- містить два конвеєри для виконання операцій з подвійною точністю, а також 54 регістри завдовжки 64 біт; чотири блоки кеш-пам'яті даних – усього 256 Кбайт;

· блок керування пам'яттю.

Цей набір кристалів містить 23 млн. транзисторів на площі 12,17 см2, виконаний за КМОП-схемотехнікою з проектними нормами 0,45 мкм, на частоті 66,5 Мгц споживає потужність 65 Вт.

Система Power РС використовує однокристальну реалізацію архітектури POWER для побудови малих машин. На основі архітектури Power РС послідовно було розроблено кристали 601 (для настільних робочих станцій), 603 (для портативних машин), 604 (для високопродуктивних настільних систем), 620 (для серверних конфігурацій з 64-бітовою організацією). У цих процесорах було внесено декілька змін у напрямках:

· спрощення архітектури з метою реалізації на однокристальних процесорах;

· виключення команд, які перешкоджають підвищенню тактової частоти;

· введення виконання команд без черги;

· розширення засобів підтримки симетричної багатопроцесорної обробки.

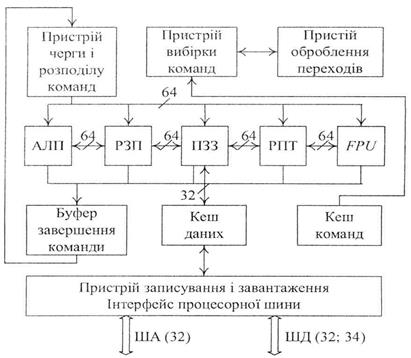

Процесор Power РС 603 містить (рис. 7.20):

· пристрій обробки переходів і вибірки команд;

· цілочисельний пристрій АЛП;

· пристрій для операцій з плаваючою комою FPU;

· кеш-пам'ять для даних і команд ємкістю по 8 Кбайт кожен;

· набір з 32 цілочисельних регістрів РЗП;

· набір з 32 регістрів РПТдля чисел з плаваючою комою;

· пристрій черги і розподілу команд;

· буфер закінчення команд;

·

|

буфери запису і завантаження.

Рис. 7.20. Структура процесора Power РС 603

Оскільки Power РС 603 є суперскалярним мікропроцесором, то він може видавати у виконавчі пристрої до трьох команд і завершувати їх виконання в одному машинному такті. Для збільшення продуктивності процесор допускає позачергове виконання команд. Окрім цього, він забезпечує програмовані режими зниження споживаної потужності.

При обробці даних команди розподіляються між п'ятьма виконавчими пристроями в заданому програмою порядку. Якщо залежності між командами відсутні, то вони виконуються миттєво.

Цілочисельне АЛП виконує більшість команд за один такт. Пристрій FPU має конвеєрну організацію і виконує операції з плаваючою комою, як з одинарною, так і з подвійною точністю.

Команди умовних переходів обробляються пристроєм переходів. Якщо умови переходу доступні, то рішення про напрямок переходу ухвалюється відразу. Інакше виконання таких команд продовжується з допущенням. Пересилки даних між кеш-пам'яттю даних і регістром РПЗ обробляються пристроями завантаження і запам'ятовування.

Після закінчення виконання команди у виконавчому пристрої її результати прямують в буфер закінчення команд. Після цього дані послідовно записуються до відповідного регістрового файлу.

Не нашли, что искали? Воспользуйтесь поиском: