ТОР 5 статей:

Методические подходы к анализу финансового состояния предприятия

Проблема периодизации русской литературы ХХ века. Краткая характеристика второй половины ХХ века

Характеристика шлифовальных кругов и ее маркировка

Служебные части речи. Предлог. Союз. Частицы

КАТЕГОРИИ:

- Археология

- Архитектура

- Астрономия

- Аудит

- Биология

- Ботаника

- Бухгалтерский учёт

- Войное дело

- Генетика

- География

- Геология

- Дизайн

- Искусство

- История

- Кино

- Кулинария

- Культура

- Литература

- Математика

- Медицина

- Металлургия

- Мифология

- Музыка

- Психология

- Религия

- Спорт

- Строительство

- Техника

- Транспорт

- Туризм

- Усадьба

- Физика

- Фотография

- Химия

- Экология

- Электричество

- Электроника

- Энергетика

Тактируемый RS-триггер

| & |

| & |

| & |

| & |

| S T C R |

| S C R |

| C S R Q |

|

| t t t t |

|

D-триггеры

| D T C |

| S T C R |

| C D Q |

| t t t |

| D C |

|

| Рис. 6.5. Триггер задержки с динамическим управлением |

| D T C |

| D T C |

| D T C |

| D C |

| а ) б ) в ) |

| Q |

| D T C |

D-триггер с динамическим управлением, тактируемый фронтом тактового импульса, можно выполнить по двухступенчатой схеме, показанной на рис. 6.5, а. Триггеры с динамическим управлением необходимы для построения счетчиков и регистров сдвига.

T-триггер

| D T C |

| T T |

| S T C R |

| T |

| T |

| Q |

| Q |

|

| Рис. 6.6. Cчетный триггер и временные диаграммы его работы |

Т-триггер (от английского Toggle – опрокидываться, кувыркаться). Он имеет только тактовый вход Т и меняет свое состояние на противоположное по фронту или срезу каждого нового тактового импульса

JK-триггер

JK-триггер выполняет наиболее универсальные функции (J – Jerk – резкое движение, толчок; K – Kill – ликвидировать). Он строится на базе RS- триггера с динамическим тактовым входом (рис. 6.7), но, в отличие от него, в JK -триггере устранено запрещенное состояние при J = K = 1. При совпадении логических единиц на информационных входах J и K он работает как счетный (режим переключения), т.е. меняет свое состояние на противоположное при каждом новом такте. Логическая 1 на входе J устанавливает триггер в состояние единицы (режим записи 1, установка), логическая 1 на входе К переводит триггер в состояние логического нуля (режим записи 0, сброс) при наличии тактирования. При наличии логических нулей на входах J и К тактовый импульс не меняет состояние триггера (режим хранения).

| J T C K |

| C Q |

| Q Q |

| K |

| J Q |

| t t t t |

| S T C R |

| & |

| & |

| J K |

| Q Q |

| Рис. 6.7. JK -триггер |

5) Разработать восьмиразрядный сумматор и цифровой компаратор.

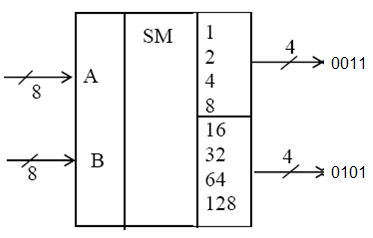

Сумматор (SM) служит для формирования арифметической суммы n-разрядных двоичных чисел А и В, в конкретном случае двух восьмиразрядных чисел

.

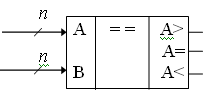

Цифровым компаратором называют устройство, фиксирующее результат сравнения n-разрядных двоичных или двоично-десятичных кодов чисел. Цифровой компаратор можно построить на сумматоре, подавая на один суммирующий вход прямой код числа А, на другой - инверсный код числа В.

6) Привести примеры восьмиканальных мультиплексоров и демультиплексоров.

Мультиплексором (от англ. Multiplexer - многократный) называют коммутатор сигналов с нескольких входов на один выход. Примеры восьмиканальных мультиплексоров представлены на рисунке 1.

Демультиплексор - коммутатор сигнала с одного входа на несколько выходов. Примеры восьмиканальных демультиплексоров представлены на рисунке 2.

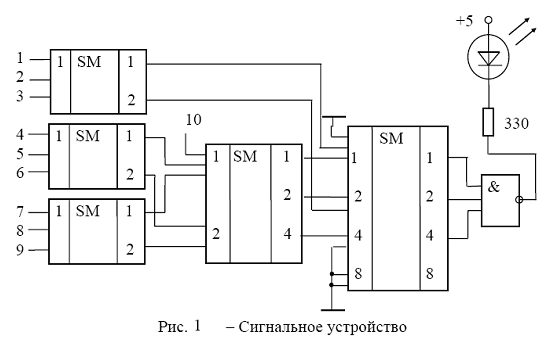

7) Разработать цифровое устройство, зажигающее светодиод при наличии логических единиц на любых M входах из 10.

Просуммируем число сработавших датчиков с помощью сумматоров (рис. 5.27), подключив датчики 1-9 к их входам с весом 1.

Логический элемент И-НЕ на выходе устройства формирует логический ноль, необходимый для того, чтобы светодиод загорелся, только при суммарном количестве сработавших датчиков, равном семи. В устройстве можно задействовать микросхемы К555ИМ5 (DD1 – 1 Столбец сумматоров), К555ИМ2 (DD2), К555ИМ6 (DD3), К555ЛА4 (DD4). Резистор задает рабочий ток светодиода порядка 10 мА.

8) Указать уровни сигналов на выходах 8-разрядного сумматора, на входы которого подаются дополнительные коды чисел минус N1 и плюс N2.

На входы сумматора подаются дополнительные коды двух чисел: +16 и -100. На выходе будет сумма этих чисел.

+16

прямой код 00010000

обратный код 00010000

дополнительный код 00010000

-100

Запишем дополнительный код однобайтового числа минус 100. Для отображения знака используется старший разряд числа.

Запишем двоичный код числа плюс 100: 01100100

Проинвертируем его: 10011011

Прибавим единицу: 10011100

Проверка: 10011100=128+16+8+4=156=256–100.

Дополнительный код числа минус 100 равен 10011100.

Просуммируем эти числа:

На рисунке изображена функциональная схема восьмиразрядного сумматора, на входы А и В которого поступают слагаемые.

Ответ: на выходе 10101100

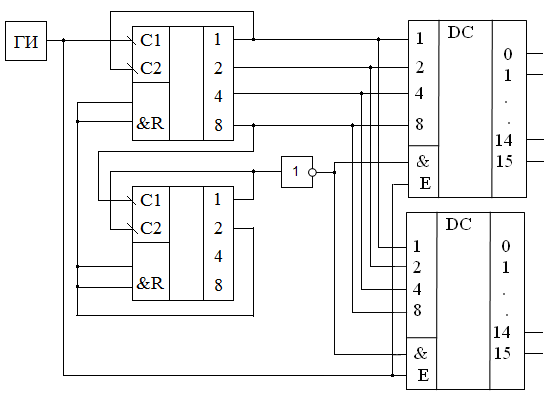

9) Разработать распределитель уровня логической единицы по N каналам.

Разработан распределитель логического уровня единицы по 32 каналам. В схеме использованы микросхемы К1533ИД3, выходы инверсные, поэтому необходимо поставить по инвертору на каждый выход, возможно использование микросхемы К555ЛН1, содержащей 6 инверторов в одном корпусе.

10) Разработать делитель частоты входных импульсов в N раз.

Счетчики с произвольным модулем счета Ксч строятся на основе микросхем двоичных и двоично-десятичных счетчиков. Одним из способов получения произвольного значения модуля счета является использование цепи обратной связи, сбрасывающей его в нулевое состояние, как только суммирующий счетчик переходит в состояние, равное Ксч.

например, с коэффициентом пересчета Ксч = 147 организован на основе восьмиразрядного двоичного счетчика (Ксч = 256), который дополнен цепью сброса. Когда счетчик переходит в состояние 147=10010011В (совпадают логические 1 на входах элементов И, подключенных к выходам счетчика с весовыми коэффициентами 128, 16, 2 и 1), происходит его сброс, в результате чего его состояния циклически повторяются через каждые 147 входных тактов.

11) Разработать коммутатор цифровых сигналов с N входов на один выход.

На рисунке 1 приведена схема коммутатора цифровых сигналов с 256 входов на один выход.

Для коммутации 256 информационных сигналов х0-х255 требуется восьмиразрядная шина адреса а0 - а7. Устройство представляет собой многоканальный мультиплексор. Выходной сигнал Y повторяет информацию того входа хi, адрес которого подан на входы а0 - а7.

Максимальное число каналов, коммутируемое одной микросхемой (например, К155КП1 или К555КП1), равно 16. Для построения устройства требуется 17 корпусов таких микросхем. Младший полубайт адреса канала подается на объединенные адресные входы микросхем DD1 - DD16. На управляющий вход Е этих микросхем подан разрешающий уровень логического нуля. Вторую ступень коммутатора образует мультиплексор DD17, на адресные входы которого подается старший полубайт адреса коммутируемого канала. При Z = 1 все каналы закрыты. При Z = 0, дважды инвертируясь, на выход проходит сигнал того канала, адрес которого зафиксирован на адресных входах а0 - а7.

12) Разработать коммутатор цифровых сигналов с одного входа на N выходов.

На приемной стороне установим четыре восьмивходовых демультиплексора, управляющие входы E которых соединим с передающей стороной. Выбор дешифратора-демультиплексора производим с помощью двух старших бит адресов А4, А3 приемной стороны. Эти адреса подаются на дополнительный дешифратор 2: 4, выходные сигналы которого поступают на входы CS ¯ (выбор микросхемы) основных дешифраторов. Выбор источника информации осуществляется младшими битами адресов А2-А1-А0 приемника.

13) Разработать распределитель уровня логического нуля по N каналам.

Разработаем распределитель логического уровня единицы по 32 каналам.

14) Аксиомы и теоремы булевой алгебры. Формы представления булевых функций.

В алгебре логики имеется четыре основных закона:

1.Переместительный закон: A+B = B+A; AB = BA.

2.Сочетательный закон:(A+B)+C=A+(B + C); (AB)C=A(BC).

3. Распределительный закон: (A+B)C = AC + BC; (AB)+C = (A + C) (B + C).

4. Закон двойственности (правило де Моргана): А + В¯ = А¯ ⋅ В¯; АВ¯ = А¯ + В¯.

Для преобразований логических выражений пользуются легко доказываемыми тождествами, вытекающими из принципа работы простейших логических элементов (аксиомы алгебры Буля):

Х+1=1; Х·1=Х; X⊕1= X¯;

X+0=Х; X·0=0; X⊕0=X;

X+X=Х; X·X=Х; X⊕X=0;

X+ X¯ =1 X⋅ X¯ =0 X⊕ X¯=1

С помощью законов алгебры логики и тождеств могут быть доказаны соотношения, получившие названия правил: поглощения: A +AB = A, A·(A +B)=A

и склеивания: A⋅B + A⋅ B ¯ = A, (A + B) · (A + B¯)=A.

Законы двойственности справедливы для любого числа переменных. В булевой алгебре при отсутствии в выражении скобок вводится следующий порядок действий: первыми выполняются операции отрицания, далее - конъюнкции, затем - дизъюнкции. Наличие в выражении скобок изменяет обычный порядок действий: в первую очередь должны выполняться операции внутри скобок. Набор логических элементов И, ИЛИ, НЕ называют основным базисом или основной функционально полной системой элементов. Последнее означает, что с помощью этих элементов можно реализовать устройство, осуществляющее сколь угодно сложную логическую операцию. Каждый из элементов И-НЕ и ИЛИ-НЕ также обладает функциональной полнотой.

15) Минимизация логических функций с помощью карт Карно: сформулировать правила, привести пример минимизации булевой функции четырех переменных.

Для упрощения логических функций трех и четырех переменных удобно использовать карты Карно. Карта Карно представляет собой прямоугольную таблицу, каждая клетка которой соответствует определенному набору таблицы истинности. На карте фиксируют область прямых значений переменных и значение логической функции для каждого набора (0,1 или Х, если функция на данном наборе не определена).

Зададим функцию с помощью выражения:

Зададим функцию с помощью выражения:

Организованные блоки по нулям выделены на карте Карно пунктирной линией, запишем минимизированное выражение для логической функции по карте Карно:

Если блоки организовать по единицам, то их число уменьшается до трех, но требуются дополнительные инверторы:

Не нашли, что искали? Воспользуйтесь поиском: