ТОР 5 статей:

Методические подходы к анализу финансового состояния предприятия

Проблема периодизации русской литературы ХХ века. Краткая характеристика второй половины ХХ века

Характеристика шлифовальных кругов и ее маркировка

Служебные части речи. Предлог. Союз. Частицы

КАТЕГОРИИ:

- Археология

- Архитектура

- Астрономия

- Аудит

- Биология

- Ботаника

- Бухгалтерский учёт

- Войное дело

- Генетика

- География

- Геология

- Дизайн

- Искусство

- История

- Кино

- Кулинария

- Культура

- Литература

- Математика

- Медицина

- Металлургия

- Мифология

- Музыка

- Психология

- Религия

- Спорт

- Строительство

- Техника

- Транспорт

- Туризм

- Усадьба

- Физика

- Фотография

- Химия

- Экология

- Электричество

- Электроника

- Энергетика

SMP в современных многоядерных процессорах

Пример: Архитектура сервера Sun SPARC Enterprise T5220

Проблема когерентности КЭШей:

Каждый процессор имеет собственную кэш-память. Наличие кэша необходимо для достижения хорошей производительности, поскольку основная память DRAM работает слишком медленно по сравнению со скоростью процессоров. Кэш работает со скоростью процессора, но эта аппаратура дорогая.

Когерентность – поддержание актуальности инф-ции.

• Для процессора кэш исполняет роль "рабочего стола", на котором хранится используемая в текущее время информация. При том, что в SMP имеется несколько устройств памяти, программное обеспечение ожидает видеть только одну общую память. Из этого следует, что если CPU1 сохраняет значение X в ячейке Q, а позже CPU2 загружает значение из ячейки Q, то CPU2 должно получить X. Но если на самом деле значение X было помещено в кэш CPU1, то как его сможет получить CPU2?

• Этот пример иллюстрирует одну из сложных проблем SMP, называемую проблемой когерентности кэшей. Если CPU2 обращается к ячейке Q, и содержимое этой ячейки отсутствует в кэше B, то через системную шину для всего компьютера посылается широковещательный запрос "У кого Q?". Все устройства кэш-памяти, ОП и даже подсистема вв/выв определяют, не у них ли находится актуальная копия Q. То устройство, которое находит актуальную копию, посылает ее процессору B.

• Поддержка когерентности серьезно влияет на производительность. Программа работает гораздо быстрее, в 10-20 раз, если используются данные, уже содержащиеся в кэше. Программы, которые обращаются к другим устройствам памяти, выполняются очень медленно.

Протоколы для SMP-систем:

• Протоколы на основе справочника (directory based). Информация о состоянии блока физической памяти содержится только в одном месте, называемом справочником (физически справочник может быть распределен по узлам системы).

• Протоколы наблюдения (snooping). Каждый кэш, который содержит копию данных некоторого блока физической памяти, имеет также соответствующую копию служебной информации о его состоянии. Централизованная система записей отсутствует. Обычно кэши расположены на общей (разделяемой) шине и контроллеры всех кэшей наблюдают за шиной (просматривают ее) для определения того, не содержат ли они копию соответствующего блока.

Пример: Протокол MESI (Modified/Exclusive/Shared/Invalid) - протокол для поддержки когерентности (согласованности) кэш-памяти процессоров в многопроцессорных системах.

- Архитектура NUMA. Принципы. Сравнение SMP и NUMA. Примеры.

NUMA архитектура Non Uniform Memory Access – неоднородный доступ к памяти

Каждый процессор имеет доступ к своей и к чужой памяти (для доступа в чужую память используется коммутационная сеть или даже проц чужого узла). Доступ к памяти чужого узла может поддерживаться аппаратно: спец. контроллеры.

Каждый процессор имеет доступ к своей и к чужой памяти (для доступа в чужую память используется коммутационная сеть или даже проц чужого узла). Доступ к памяти чужого узла может поддерживаться аппаратно: спец. контроллеры.

-: дорого, плохая масштабируемость.

Сейчас: NUMA осущ доступ к чужой памяти программно.

Архитектура NUMA - гибридная архитектура воплощает в себе удобства SMP и относительную дешевизну MPP.

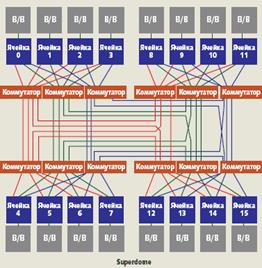

• Вычислительная система NUMA состоит из набора узлов (содержит один или несколько процессоров, на нем работает единственная копия ОС), которые соединены между собой коммутатором либо быстродействующей сетью.

• Топология связей разбивается на несколько уровней. Каждый из уровней предоставляет соединения в группах с небольшим числом узлов. Такие группы рассматриваются как единые узлы на более высоком уровне. На данный момент созданы ВС с 2-уровневыми схемами связей.

• ОП физически распределена, но логически общедоступна.

• В зависимости от пути доступа к элементу данных, время, затрачиваемое на эту операцию, может существенно различаться.

• Примеры конкретных реализаций: cc-NUMA, СОМА, NUMA-Q и т.п.

Суть этой архитектуры - в особой организации памяти: память является физически распределенной по различным частям системы, но логически разделяемой, так что пользователь видит единое адресное пространство.

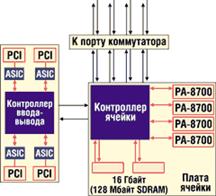

Система состоит из однородных базовых модулей (плат), состоящих из небольшого числа процессоров и блока памяти.

Модули объединены с помощью высокоскоростного коммутатора. Поддерживается единое адресное пространство, аппаратно поддерживается доступ к удаленной памяти, т.е. к памяти других модулей.

При этом доступ к локальной памяти осуществляется в несколько раз быстрее, чем к удаленной.

По существу архитектура NUMA похожа на MPP архитектуру, где в качестве отдельных вычислительных элементов берутся SMP узлы.

Пример: HP Integrity SuperDome (Осн эл-т арх Superdome, Межсоединения в Superdome)

Не нашли, что искали? Воспользуйтесь поиском: