ТОР 5 статей:

Методические подходы к анализу финансового состояния предприятия

Проблема периодизации русской литературы ХХ века. Краткая характеристика второй половины ХХ века

Характеристика шлифовальных кругов и ее маркировка

Служебные части речи. Предлог. Союз. Частицы

КАТЕГОРИИ:

- Археология

- Архитектура

- Астрономия

- Аудит

- Биология

- Ботаника

- Бухгалтерский учёт

- Войное дело

- Генетика

- География

- Геология

- Дизайн

- Искусство

- История

- Кино

- Кулинария

- Культура

- Литература

- Математика

- Медицина

- Металлургия

- Мифология

- Музыка

- Психология

- Религия

- Спорт

- Строительство

- Техника

- Транспорт

- Туризм

- Усадьба

- Физика

- Фотография

- Химия

- Экология

- Электричество

- Электроника

- Энергетика

Динамические D-триггеры.

Фронт сигнала синхронизации, в отличие от высокого (или низкого) потенциала, не может длиться продолжительное время. В идеале длительность фронта равна нулю. Поэтому в триггере, запоминающем входную информацию по фронту не нужно предъявлять требования к длительности тактового сигнала.

Триггер, запоминающий входную информацию по фронту синхронизирующего сигнала, может быть построен из двух триггеров, работающих по потенциалу. Сигнал синхронизации будем подавать на эти триггеры в противофазе. Для формирования такого синхронизирующего сигнала воспользуемся инвертором. Принципиальная схема двухтактного триггера приведена на рисунке 8.15.

Рисунок 8.15 – Схема динамического D‑триггера

Рассмотрим работу этой схемы подробнее. Для этого воспользуемся временными диаграммами, приведёнными на рисунке 8.17. На этих временных диаграммах обозначение Q΄ соответствует сигналу на выходе первого триггера. Так как на вход синхронизации триггеров тактовый сигнал поступает через инвертор, то когда первый триггер находится в режиме хранения, второй триггер пропускает сигнал на выход схемы. И наоборот, когда первый триггер пропускает сигнал с входа схемы на свой выход, второй триггер находится в режиме хранения.

Обратите внимание, что сигнал на выходе всей схемы в целом не зависит от сигнала на входе “D” схемы. Если первый триггер пропускает сигнал данных со своего входа на выход, то второй триггер в это время находится в режиме хранения и поддерживает на выходе предыдущее значение сигнала, то есть сигнал на выходе схемы тоже не может измениться.

Из приведенного выше анализа видно, что сигнал в схеме, приведенной на рисунке 8.15, запоминается в момент изменения сигнала на синхронизирующем входе “C” с единичного потенциала на нулевой.

Динамические D‑триггеры выпускаются в виде готовых микросхем или входят в виде готовых блоков в составе больших интегральных схем, таких как базовый матричный кристалл (БМК) или программируемых логических интегральных схем (ПЛИС). Условно-графическое обозначение динамического D‑триггера, запоминающего информацию по фронту тактового сигнала, приведено на рисунке 8.16.

Рисунок 8.16 – Условно-графическое обозначение D‑триггера

Рисунок 8.17 – Временные диаграммы D‑триггера

То, что триггер запоминает входной сигнал по фронту, отображается на условно-графическом обозначении треугольником, изображённым на выводе входа синхронизации. То, что внутри этого триггера находится два триггера, отображается двойной буквой T в среднем поле условно-графического изображения. Иногда при изображении динамического входа указывают, по какому фронту триггер изменяет своё состояние. В этом случае используется обозначение входа синхронизации, как это показано на рисунке 8.18.

Рисунок 8.18 – Обозначение динамических входов

На рисунке 8.18 а обозначен динамический вход, работающий по переднему (нарастающему) фронту сигнала. На рисунке 8.18 б обозначен динамический вход, работающий по заднему (спадающему) фронту сигнала. Промышленностью выпускаются готовые микросхемы, содержащие динамические триггеры. В качестве примера можно назвать микросхему 1533ТМ2. В этой микросхеме содержится сразу два динамических триггера. Они изменяют своё состояние по переднему фронту сигнала синхронизации.

Т-триггер.

Т-триггер – это счетный триггер, у которого имеется только один вход. После поступления на этот вход импульса, состояние Т-триггера меняется на прямо противоположное. Счётным триггер называется потому, что он как бы подсчитывает количество импульсов, поступивших на его вход. Жаль только, что считать этот триггер умеет только до одного. При поступлении второго импульса T‑триггер снова сбрасывается в исходное состояние.

Т-триггеры строятся только на базе двухступенчатых триггеров, подобных рассмотренному ранее D‑триггеру. Использование двух триггеров позволяет избежать самовозбуждения схемы, так как счетные триггеры строятся при помощи схем с обратной связью.

Т-триггер можно синтезировать из любого двухступенчатого триггера. Рассмотрим пример синтеза Т-триггера из динамического D‑триггера. Для того чтобы превратить D‑триггер в счётный Т-триггер, необходимо ввести цепь обратной связи с инверсного выхода D‑триггера на его вход данных D, как это показано на рисунке 8.19.

Рисунок 8.19 – Схема T‑триггера, построенная на основе D‑триггера

Временная диаграмма T‑триггера приведена на рисунке 8.20. При построении этой временной диаграммы был использован D‑триггер, работающий по заднему фронту синхронизирующего сигнала.

Рисунок 8.20 – Временные диаграммы T‑триггера

Т‑триггеры используются при построении схем различных счётчиков, поэтому в составе программируемых БИС обычно есть готовые модули этих триггеров. Условно-графическое обозначение T‑триггера на принципиальных схемах приведено на рисунке 8.20.

Рисунок 8.21 – Условно-графическое обозначение T‑триггера

Так как T‑триггеры легко получить из D-триггера или JK‑триггера, который будет рассмотрен в следующем разделе, то отдельные микросхемы T‑триггеров промышленностью не выпускаются.

JK‑триггер.

Прежде чем начать изучение JK‑триггера, вспомним принципы работы RS‑триггера. Напомним, что в этом триггере есть запрещённые комбинации входных сигналов. Одновременная подача единичных сигналов на входы сброса R и и установки единицы S запрещена. JK‑триггер устраняет этот недостаток.

Таблица истинности JK‑триггера практически совпадает с таблицей истинности синхронного RS‑триггера. Для того чтобы исключить запрещённое состояние, схема триггера изменена таким образом, что при подаче двух единиц JK‑триггер превращается в счётный триггер. Это означает, что при подаче на тактовый вход C импульсов JK‑триггер изменяет своё состояние на противоположное. Таблица истинности JK‑триггера приведена в таблице 8.6.

Таблица 8.6 – Таблица истинности JK‑триггера.

| С | K | J | Q(t) | Q(t+1) | Пояснения |

| x | x | Режим хранения информации | |||

| x | x | ||||

| Режим хранения информации | |||||

| Режим установки единицы J=1 | |||||

| Режим записи нуля K=1 | |||||

| R=S=1 запрещенная комбинация | |||||

Один из вариантов внутренней схемы JK-триггера приведен на рисунке 8.22.

Рисунок 8.22 – Внутренняя схема JK‑триггера

Для реализации счетного режима в схеме, приведенной на рисунке 8.22, введена перекрестная обратная связь с выходов второго триггера на входы R и S первого триггера. Благодаря этой обратной связи на входах R и S никогда не может возникнуть запрещенная комбинация.

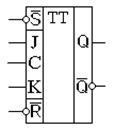

Приводить временные диаграммы работы JK‑триггера не имеет смысла, так как они совпадают с приведёнными ранее диаграммами RS‑ и T‑триггера. Условно-графическое обозначение JK‑триггера изображено на рисунке 8.23.

Рисунок 8.23 – Условно-графическое обозначение JK‑триггера

На этом рисунке приведено обозначение типовой цифровой микросхемы JK-триггера, выполненной по ТТЛ технологии. В промышленно выпускающихся микросхемах обычно кроме входов JK‑триггера реализуются входы RS‑триггера, которые позволяют устанавливать триггер в заранее определённое исходное состояние.

В названиях отечественных микросхем для обозначения JK-триггера присутствуют буквы ТВ. Например, микросхема К1554ТВ9 содержит в одном корпусе два JK-триггера. В качестве примеров иностранных микросхем, содержащих JK-триггеры можно назвать такие микросхемы, как 74HCT73 или 74ACT109.

Так как JK‑триггер является универсальной схемой, то рассмотрим несколько примеров использования этого триггера. Начнем с примера использования JK‑триггера в качестве обнаружителя коротких импульсов.

Рисунок 8.24 – Схема обнаружения короткого импульса

В данной схеме при поступлении на вход “C” импульса триггер переходит в единичное состояние, которое затем может быть обнаружено последующей схемой (например, микропроцессором). Для того, чтобы привести схему в исходное состояние, необходимо подать на вход R уровень логического нуля.

Теперь рассмотрим пример построения на JK‑триггере ждущего мультивибратора. Один из вариантов подобной схемы приведен на рисунке 8.25.

Рисунок 8.25 – Схема ждущего мультивибратора

Схема работает подобно предыдущей схеме. Длительность выходного импульса определяется постоянной времени RC цепочки. Диод VD1 предназначен для быстрого восстановления исходного состояния схемы (разряда емкости C). Если быстрое восстановление схемы не требуется, например, когда длительность выходных импульсов гарантированно меньше половины периода следования входных импульсов, то диод VD1 можно исключить из схемы ждущего мультивибратора.

В качестве последнего примера применения универсального JK‑триггера, рассмотрим схему счетного T‑триггера. Схема счетного триггера приведена на рисунке 8.26.

Рисунок 8.26 – Схема счетного триггера, построенного на JK‑триггере

В схеме, приведенной на рисунке 8.26, для реализации счетного режима работы триггера на входы J и K подаются уровни логической единицы.

Регистры

Регистром называется последовательное или параллельное соединение нескольких триггеров. Регистры обычно строятся на основе D триггеров. При этом для построения регистров могут использоваться как динамические, так и статические D триггеры (триггеры-защелки). Количество триггеров в составе регистра определяет его разрядность. В качестве отдельных микросхем обычно используются четырех- или восьмиразрядные триггеры.

Не нашли, что искали? Воспользуйтесь поиском: