ТОР 5 статей:

Методические подходы к анализу финансового состояния предприятия

Проблема периодизации русской литературы ХХ века. Краткая характеристика второй половины ХХ века

Характеристика шлифовальных кругов и ее маркировка

Служебные части речи. Предлог. Союз. Частицы

КАТЕГОРИИ:

- Археология

- Архитектура

- Астрономия

- Аудит

- Биология

- Ботаника

- Бухгалтерский учёт

- Войное дело

- Генетика

- География

- Геология

- Дизайн

- Искусство

- История

- Кино

- Кулинария

- Культура

- Литература

- Математика

- Медицина

- Металлургия

- Мифология

- Музыка

- Психология

- Религия

- Спорт

- Строительство

- Техника

- Транспорт

- Туризм

- Усадьба

- Физика

- Фотография

- Химия

- Экология

- Электричество

- Электроника

- Энергетика

Основные блоки микросхем цифровой обработки сигналов

В настоящее время получили распространение схемы, в которых выходной сигнал формируется непосредственно в цифровой форме. Затем этот сигнал преобразуется в аналоговую форму при помощи цифро-аналогового преобразователя. В составе этих микросхем широко используются сумматоры, умножители и цифровые фильтры. Изучение устройств прямого цифрового синтеза начнём с простейшего устройства обработки цифровых сигналов – двоичного сумматора.

Двоичные сумматоры

Важным элементом цифровых устройств, выполняющих арифметическую обработку цифровой информации, является сумматор. Построение двоичных многоразрядных сумматоров обычно начинается с одноразрядного сумматора по модулю 2. В таблице 15.1 приведена таблица истинности этого сумматора. Ее можно получить, исходя из правил суммирования одиночных бит в двоичной арифметике, которые мы рассматривали ранее.

Таблица 15.1 – Таблица истинности сумматора по модулю 2

| Вход X | Вход Y | Выход |

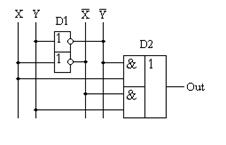

В соответствии с принципами реализации принципиальноый схемы по произвольной таблице истинности, рассмотренными в предыдущих главах, получим принципиальную схему сумматора по модулю 2. Формирование этой схемы ничем не отличается от предыдущих примеров, рассмотренных ранее. Как и раньше выделяем строки содержащие единицу в выходном сигнале. Они реализуются элементами "2И". Нулевые потенциалы входных сигналов в этих строках превращаются в единичные при помощи инверторов. Объединение выходов логических элементов в один производится логическим элементом "2ИЛИ". Полученная принципиальная схема сумматора по модулю 2 приведена на рисунке 15.1.

Рисунок 15.1 – Принципиальная схема, реализующая таблицу истинности сумматора по модулю 2

Сумматор по модулю 2 (для двух входов его схема полностью совпадает со схемой исключающего "ИЛИ") изображается на принципиальных схемах как показано на рисунке 15.2.

Рисунок 15.2 – Условно-графическое обозначение схемы, выполняющей логическую функцию "исключающего ИЛИ"

Сумматор по модулю 2 выполняет суммирование без учета переноса между двоичными разрядами. В полном двоичном сумматоре его необходимо учитывать, поэтому требуются элементы, позволяющие формировать перенос в следующий двоичный разряд. Таблица истинности такого устройства, называемого полусумматором, приведена в таблице 15.2.

Обратите внимание, что сигналы в приведенной таблице истинности расположены в порядке, принятом для схем, то есть в соответствии с тем, что сигнал распространяется слева направо. В результате перенос, который имеет двоичный вес больший, по сравнению с суммируемыми разрядами записан правее. В математике принят другой порядок разрядов числа. Старший разряд на бумаге записывается самым левым, а младший разряд записывается самым правым. В результате может возникнуть путаница. Чтобы этого не произошло, приведу десятичный эквивалент каждой строки таблицы истинности полусумматора (таблица 15.2).

Первая строка этой таблицы истинности получена из арифметического выражения 0+0=010(002). Вторая строка получена из арифметического выражения 0+1=110(012). Третья строка получена из арифметического выражения 1+0=110(012). Четвертая строка получена из арифметического выражения 1+1=210(102).

Таблица 15.2 – Таблица истинности полусумматора

| Вход A | Вход B | Выход S | Выход PO | Математическое выражение |

| 0+0=010 (002) | ||||

| 0+1=110 (012) | ||||

| 1+0=110 (012) | ||||

| 1+1=210 (102) |

В соответствии с принципами построения произвольной таблицы истинности получим принципиальную схему полусумматора. Схема, соответствующая таблице истинности, содержащейся в таблице 15.2, приведена на рисунке 15.3.

Рисунок 15.3 – Принципиальная схема цифрового устройства, реализующего таблицу истинности полусумматора

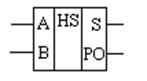

Полусумматоры выпускаются в виде отдельных микросхем и используются в качестве отдельных модулей в составе больших интегральных микросхем, поэтому ГОСТом предусмотрено условно-графическое обозначение полусумматора. Оно приведено на рисунке 15.4.

Рисунок 15.4 – Условно-графическое обозначение полусумматора

Полусумматор формирует перенос в следующий разряд, но не может учитывать перенос из предыдущего разряда, поэтому он и называется полусумматором. В результате такой особенности полусумматор не может использоваться в качестве отдельного устройства. Практический интерес представляет полный сумматор.

Таблицу истинности полного одноразрядного двоичного сумматора (таблица 15.3), как и таблицу истинности полусумматора, можно получить из правил арифметического суммирования двоичных чисел. В обозначении входов и выходов полного сумматора использовано следующее правило: в качестве входов использованы одноразрядные двоичные числа A и B; сумма — это одноразрядное двоичное число S; перенос обозначен буквой P; для обозначения входа переноса используется сочетание букв PI (I — сокращение от английского слова input, вход); для обозначения выхода переноса используется сочетание букв PO (O — сокращение от английского слова output, выход).

Таблица 15.3 – Таблица истинности полного двоичного

одноразрядного сумматора

| № | PI | A | B | S | PO | Математическое выражение |

| 0+0+0=010 (002) | ||||||

| 0+0+1=110 (012) | ||||||

| 0+1+0=110 (012) | ||||||

| 0+1+1=210 (102) | ||||||

| 1+0+0=110 (012) | ||||||

| 1+0+1=210 (102) | ||||||

| 1+1+0=210 (102) | ||||||

| 1+1+1=310 (112) |

Теперь, точно так же как и в предыдущих случаях, соответствии с правилами построения принципиальной схемы по произвольной таблице истинности получим схему полного двоичного одноразрядного сумматора. Схема, соответствующая таблице истинности, содержащейся в таблице 14.3, приведена на рисунке 15.5. Эта схема построена с использованием СДНФ.

Рисунок 15.5 – Принципиальная схема, реализующая таблицу истинности полного двоичного одноразрядного сумматора

Схему полного одноразрядного сумматора можно минимизировать. Для этого достаточно посмотреть на две последние строки его таблицы истинности. Мы можем увидеть, что сигнал переноса в них не зависит от сигнала, присутствующего на входе B. Поэтому этот вход можно не заводить на вход схемы "И".

В результате описанных рассуждений вместо двух нижних элементов"3И" можно воспользоваться одним двухвходовым элементом "2И". Точно такая же ситуация возникает если рассмотреть строки 6 и 8. В этом случае лишним оказывается вход A. То есть и в этом случае можно обойтись одним двухвходовым логическим элементом "2И".

Вход PI оказывается лишним в выражениях, описывающих строки 4 и 8. В результате описанных действий принципиальная схема формирования переноса в следующий разряд сумматора упрощается, и приобретает вид, приведённый на рисунке 15.6.

Рисунок 15.6 – Минимизированная принципиальная схема, реализующая таблицу истинности полного двоичного одноразрядного сумматора

Примером одноразрядного двоичного сумматора может служить микросхема средней интеграции К155ИМ1. Условно-графическое обозначение полного двоичного одноразрядного сумматора показано на рисунке 15.7.

Рисунок 15.7 – Условно-графическое изображение полного двоичного одноразрядного сумматора

Однако для выполнения вычислений в схемах цифровой обработки сигналов недостаточно точности одноразрядного сумматора. В них применяются 16- или даже 40-разрядные двоичные сумматоры.

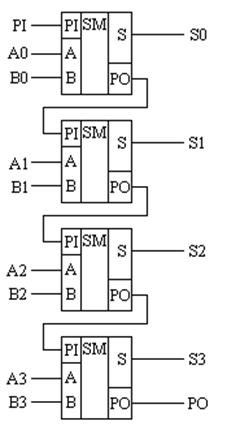

Для того чтобы получить многоразрядный сумматор из полученного выше одноразрядного сумматора, достаточно соединить входы и выходы переносов соответствующих двоичных разрядов. Принципиальная схема четырехразрядного сумматора, реализованная на четырех одноразрядных сумматорах, приведена на рисунке 15.8.

Рисунок 15.8 – Принципиальная схема четырехразрядного двоичного сумматора

На приведенной схеме двоичный вес разрядов суммируемых чисел A и B отображен непосредственно в названии цепи. Например, цепь A0 передает нулевой разряд числа A, цепь B2 передает второй разряд числа B. Названия входа PI и выхода переноса PO не изменены.

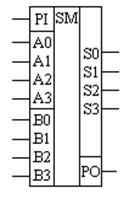

Полный двоичный четырехразрядный сумматор изображается на схемах с использованием условно-графического обозначения, показанного на рисунке 15.9. Обратите внимание, что в этом обозначении входы двоичного слова A объединены в отдельное поле. Точно так же объединены входы двоичного слова B. Вход и выход сигналов переноса на приведенном условно-графическом обозначении микросхемы тоже выделены в отдельные поля. Изображённая таким образом микросхема намного более наглядно отображает свои функции.

Рисунок 15.9 – Условно-графическое обозначение полного двоичного 4-разрядного сумматора на схемах

Приведенная на рисунке 15.8 схема не оптимизирована по быстродействию, она служит лишь для пояснения принципа действия многоразрядного двоичного сумматора. В применяемых на практике схемах никогда не допускают последовательного распространения переноса через все разряды многоразрядного сумматора, так как это снижает его быстродействие.

Для увеличения скорости работы двоичного сумматора используется отдельная схема формирования переносов для каждого двоичного разряда. Таблицу истинности для такой схемы легко получить из алгоритма суммирования двоичных чисел, а затем применить хорошо известные нам принципы построения цифрового устройства по произвольной таблице истинности.

Следующим, широко используемым в схемах цифровой обработки сигналов устройством, является цифровой двоичный умножитель. Эти устройства используются как в схемах масштабирования (усилители или аттенюаторы) или гетеродинирования сигналов, так и в составе цифровых фильтров.

Не нашли, что искали? Воспользуйтесь поиском: