ТОР 5 статей:

Методические подходы к анализу финансового состояния предприятия

Проблема периодизации русской литературы ХХ века. Краткая характеристика второй половины ХХ века

Характеристика шлифовальных кругов и ее маркировка

Служебные части речи. Предлог. Союз. Частицы

КАТЕГОРИИ:

- Археология

- Архитектура

- Астрономия

- Аудит

- Биология

- Ботаника

- Бухгалтерский учёт

- Войное дело

- Генетика

- География

- Геология

- Дизайн

- Искусство

- История

- Кино

- Кулинария

- Культура

- Литература

- Математика

- Медицина

- Металлургия

- Мифология

- Музыка

- Психология

- Религия

- Спорт

- Строительство

- Техника

- Транспорт

- Туризм

- Усадьба

- Физика

- Фотография

- Химия

- Экология

- Электричество

- Электроника

- Энергетика

Структурное представление цифровых устройств

На основе функциональных моделей и схем строятся структурные схемы. на начальном этапе строится обобщенная структурная схема. На рисунке 2.7 показана обобщенная структурная схема подсистемы управления приводом подачи станка с салазками.

Далее строится детальная структурная схема ЦУ.

Рассмотрим процесс проектирования на примере регистра, построенного на триггерах.

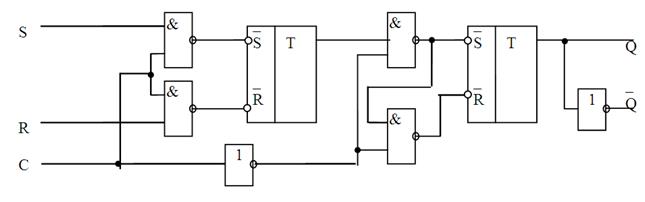

Необходимо спроектировать регистр на основе двухступенчатого триггера. В силу отсутствия в серии микросхем двухступенчатого триггера возникает необходимость в его синтезе с использованием имеющихся элементов малой интеграции и RS-триггера. В серии 555 имеется RS-триггер без синхронизирующего входа 555TР2. На его основе синтезируем схему блока триггера, изображенную на рисунке 2.4.

Рисунок 2.8 – Структурная схема двухступенчатого триггера на базе RS-блоков

Полученная схема двухступенчатого триггера обеспечивает переключение триггера по заднему фронту тактового импульса, т.е. запись данных в первую ступень триггера происходит по переднему фронту тактового импульса, а появление данных на выходе – по заднему фронту. Этим достигается устойчивость работы триггера и исключается возможность его повторного переключения в течение тактового импульса и формирование на его выходах неверных данных.

Проектирование микроопераций двухступенчатого триггера.

При подаче тактового импульса на синхронизирующие входы триггеров и при разрешении операции обнуления (Y=0) по заднему фронту импульса, информация, находящаяся на входах триггеров переписывается на их выходы, т.о. обнуление триггеров происходит в том случае, если к моменту подачи тактового импульса на R-входах триггеров установлены уровни логической единицы, а на S-входах – уровни логического нуля.

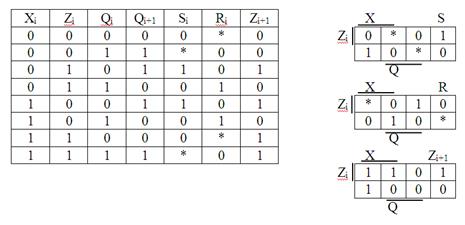

Рисунок 2.9 - Таблицы истинности триггера при сбросе

Микрооперация записи данных.

Когда операция записи данных разрешена, т.е. Y =1, и при подаче на синхровходы триггеров тактового импульса С по его заднему фронту, информация, находящаяся на входах триггеров, переписывается в ячейки памяти дискретного устройства и появляется на выходах Qi. При изменении входных данных, т.е. при переключении сигналов X i они с задержкой распространения импульса по цепям микросхем, участвующих в микрооперации записи данных, появляются на входах триггеров. При подаче следующего тактового импульса С микрооперация записи данных повторяется.

Рисунок 2.10- Таблицы истинности триггера при записи

Когда Y =2, по заднему фронту тактового импульса информация со входов триггера поступает на их выходы, а затем осуществляется сдвиг кода, хранящегося в данный момент в ячейках памяти, в сторону младших разрядов т.е. влево. При сдвиге каждый запоминающий элемент должен:

- передать хранимую информацию на элемент Ti-1

- изменить свое состояние за счет приема информации от триггера Т i+1 при сдвиге на один разряд влево.

Передача от триггера Тi и изменение его состояния не могут проходить одновременно. В данном курсовом проекте эта трудность исключается за счет использования синхронных двухступенчатых RS-триггеров с динамическим управлением записью. Внутренняя организация таких триггерных схем предусматривает разделение во времени этапов приема входной информации и смены выходной. В них по переднему фронту синхронизирующего сигнала происходит прием информации, а по заднему - изменение состояния.

Рисунок 2.11 - Таблицы истинности триггера при сдвиге

В данном дискретном устройстве разрабатывается логическая микрооперация - дизъюнкция. Когда Y=3 и на синхровходы триггеров подается тактовый импульс выполняется заданная логическая операция над содержимым ячейки памяти и входными данными.

Рисунок 2.12 - Таблицы истинности триггера при логических операциях

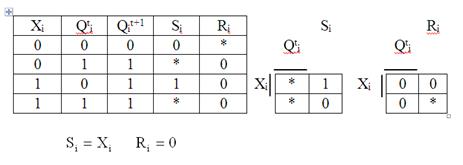

В данном дискретном устройстве разработана арифметическая операция вычитания. Анализируя исходное состояние триггера, перенос, в соответствии со словарем переходов RS-триггеров составляем таблицу (рисунок 2.8).

Функции возбуждения триггера для данной операции имеют следующий вид:

, (1)

, (1)

Рисунок 2.13 - Таблицы истинности триггера вычитании

Построение функций возбуждения триггеров

Построение объединенных функций возбуждения триггеров реализуется следующим образом:

- построение объединенной таблицы функционирования для каждой микрооперации и каждого установочного входа триггера;

запись функций возбуждения.

Быстродействие дискретного устройства следует оценивать по максимальной частоте тактовых импульсов, поступающих на синхронизирующий вход. Максимальная частота тактовых импульсов – это максимально допустимая частота подаваемых в дискретное устройство импульсов, не приводящих к нарушению его работы. Таблица 2.1 является объединенной таблицей функционирования ЦУ. В ней строки соответствуют микрооперациям, а столбцы установочным входам триггеров. Для каждого установочного входа записывается функция возбуждения.

Таблица 2.1 - Объединенная таблица функционирования ЦУ

| Опер. | S0 | R0 | S1 | R1 | S2 | R2 | S3 | R3 |

| Y0 | X0 |

| X1 |

| X2 |

| X3 |

|

| Y1 | Q1 |

| Q2 |

| Q3 |

| Pвх |

|

| Y2 | X0 | X1 | X2 | X3 | ||||

| Y3 |

|

|

|

|

|

|

|

|

| Y4 |

|

|

|

|

|

|

|

|

| Y5 |

|

|

|

|

|

|

|

|

| Y6 |

На основании оставленной таблицы синтезируем функции возбуждения триггеров:

, (2)

, (2)

В общем случае для расчета максимальной тактовой частоты необходимо определить минимальные длительности тактового импульса и паузы между тактовыми импульсами. Тогда частоту fmax можно определить по формуле:

, (3)

, (3)

Длительность такта для синхронных схем дискретного устройства определяется исходя из быстродействия используемого триггера. Длительность паузы между тактовыми импульсами определяется временем переходного процесса в дискретном устройстве и оценивается максимальной длиной функциональной цепи:

, (4)

, (4)

где  – максимальная задержка сигнала на одном элементе;

– максимальная задержка сигнала на одном элементе;

n – число уровней функциональной цепи (глубина КСх).

Вычисляем максимальную тактовую частоту дискретного устройства:

Выполняя инвертирование сигнала на входах триггеров мы добиваемся того, что подача напряжений одинаковых уровней на входы S и R невозможна. Значит, при S = 0, R = 1 – на выходе получим 0, при S = 1, R = 0 – на выходе получим 1. На входах сдвигающего регистра необходимо установить четыре элемента со следующей таблицей истинности (Таблица 2.2).

Соединив четвёртый выход с первым входом мы получаем кольцевой право-сдвигающий регистр. Информация с выхода Q4 не будет теряться, а будет циркулировать заново

Таблица 2.2- Таблица истинности проектируемого регистра

| Х1 | Х2 | Y |

Поскольку такой регистр сдвига четырёхразрядный, количество возможных комбинаций на входе составит 16. Рассмотрим работу нашего регистра при подаче на вход некоторых комбинаций.(таблица 2.3)

Таблица 2.3 – Принцип работы проектируемого устройства

| № комбинации | Вход | Выход | |||||||

| D1 | D2 | D3 | D3 | № импульса | Q1 | Q2 | Q3 | Q4 | |

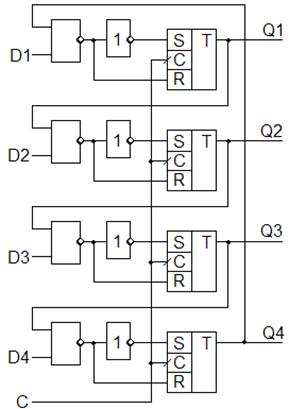

Рисунок 2.14 - Схема право-сдвигающего синхронного регистра на RS-триггерах

Разработаем четырёхфазный регистр сдвига на RS-триггерах. Пусть он будет правосдвигающим. Для этого нам понадобится четыре синхронных RS-триггера с синхронизацией по фронту тактирующего импульса и некоторое число логических элементов для создания цепей переноса. Так как сдвигающие регистры с последовательными входом и выходом имеют низкое быстродействие, разработаем схему с параллельными входом и выходом.

Не нашли, что искали? Воспользуйтесь поиском: