ТОР 5 статей:

Методические подходы к анализу финансового состояния предприятия

Проблема периодизации русской литературы ХХ века. Краткая характеристика второй половины ХХ века

Характеристика шлифовальных кругов и ее маркировка

Служебные части речи. Предлог. Союз. Частицы

КАТЕГОРИИ:

- Археология

- Архитектура

- Астрономия

- Аудит

- Биология

- Ботаника

- Бухгалтерский учёт

- Войное дело

- Генетика

- География

- Геология

- Дизайн

- Искусство

- История

- Кино

- Кулинария

- Культура

- Литература

- Математика

- Медицина

- Металлургия

- Мифология

- Музыка

- Психология

- Религия

- Спорт

- Строительство

- Техника

- Транспорт

- Туризм

- Усадьба

- Физика

- Фотография

- Химия

- Экология

- Электричество

- Электроника

- Энергетика

Программируемые вентильные матрицы (FPGA). Структура блока типа SLICEL в FPGA Spartan3.

Микросхемы программируемых пользователями вентильных матриц FPGA (Field Programmable Gate Arrays) в своей основе состоят из большого числа конфигурируемых логических блоков (КЛБ), расположенных по строкам и столбцам в виде матрицы, и трассировочных ресурсов, обеспечивающих их соединения. В архитектуре FPGA явно прослеживается большое сходство с архитектурой БМК. Разница в том, что FPGA, поступающая в распоряжение потребителя, имеет уже готовые, стандартные, хотя и не запрограммированные, трассировочные ресурсы, не зависящие от потребителя. Конкретный проект на базе FPGA реализуется программированием соединений, в ходе которого на кристалле создается требуемая схема. Обращаться к изготовителю FPGA при этом не требуется.

Типичная FPGA представляет собой микросхему высокого уровня интеграции, содержащую во внутренней области матрицу идентичных функциональных блоков и систему их соединений, размещенную между строками и столбцами матрицы, а в периферийной области — блоки ввода/вывода (в наиболее сложных FPGA стали появляться и варианты с более свободным расположением блоков ввода/вывода).

Такая структура подобна канальным БМК. Различие, имеющее важнейшее принципиальное значение, состоит в том, что для FPGA все производственные процессы изготовления кристалла, требующие изготовления фотошаблонов и проведения сложных технологических операций, уже закончены, и реализация конкретного проекта находится целиком в руках системотехника и осуществляется простыми средствами.

Основные части FPGA:

- функциональные блоки;

- система межсоединений;

- блоки ввода/вывода.

Все эти части конфигурируются или реконфигурируются самими пользователями.

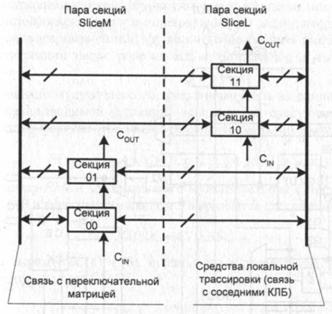

Обновленные схемы ФБ были применены фирмой Xilinx сначала в сериях Virtex, а затем Spartan. Рассмотрим структуру и работу этих конфигурируемых логических блоков КЛБ (CLB, Configurable Logic Blocks) на примере микросхем Spartan-3. Блоки состоят из четырех секций (Slice), сгруппированных в две пары.

Пара SliceL составлена из секций, выполняющих логические или арифметические операции, а также функции постоянного ЗУ. Пара SliceM содержит секции, способные дополнительно к перечисленным выполнять также функции оперативного запоминающего устройства ОЗУ и 16-разрядного регистра сдвига. В каждой паре секций организуется цепь быстрого переноса со входом Cin и выходом Cout.

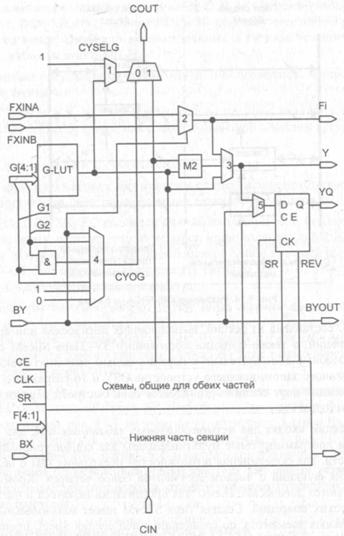

В состав секции входят два четырехвходовых табличных ФП, два регистра (триггера) и программируемые мультиплексоры для конфигурирования схем и, в частности, для объединения возможностей нескольких ФП с целью воспроизведения функций с числом аргументов более четырех. Кроме того, в секциях имеются логические схемы для организации переноса и выполнения арифметических операций. Секция типа SliceM имеет максимальный набор функциональных элементов, по сравнению с ней секция SliceL проще, т. к. в ней не реализуются ОЗУ и регистр сдвига. Секция разделена на три части: верхнюю, нижнюю и общую для обеих частей. Верхняя часть раскрыта до вентильного уровня и в ней показаны цепи, реализующие логические операции. Для секции, в которой предусмотрены режимы ОЗУ и регистра сдвига, к показанным на рисунке элементам добавляется еще несколько, причем в основном в общей части, где в этом случае вырабатываются сигналы управления ОЗУ или регистром сдвига.

В каждой из идентичных частей секции имеется LUT-блок (G — в верхней части и F — в нижней с входными сигналами G[4:l] и F[4:l] соответственно). В каждой части имеется также триггер (регистр) типа D, который можно сконфигурировать как управляемый фронтом (flip-flop) или уровнем сигнала (latch). Кроме того, в обеих частях имеются программируемые мультиплексоры и по два логических элемента (конъюнктор и элемент сложения по модулю два). Мультиплексоры конфигурируют схему, но два из них (по одному в каждой из частей) имеют при этом специфическую задачу наращивания числа аргументов воспроизводимой функции (wide-function multiplexers). Для верхней части секции такую роль играет мультиплексор 2, выход которого обозначен как Fi.

Для верхней части секции подфункции поступают на мультиплексор 2 со входов FXINA и FXINB извне (от других секций). Они могут зависеть от разного числа аргументов. Выходная функция обозначена как Fi, причем индекс i может быть равным 6, 7 или 8. При этом к числу аргументов, от которых зависят FXINA и FXINB, добавляется переменная BY. В нижней части секции выход аналогичного по назначению мультиплексора обозначен как F5, т.е. как функция, которая имеет конкретное число аргументов — пять. Это объясняется тем, что здесь на мультиплексор поступают не внешние сигналы (функции с неизвестным заранее числом аргументов), а выходы обоих LUT-блоков самой секции, т.е. функции не более чем четырех аргументов.

Цепь переноса сконструирована для поддержки выполнения совместно с логическими вентилями (И, М2) математических операций с высокой скоростью. Она управляется несколькими мультиплексорами и имеет ряд вариантов функционирования. К их числу относятся простое пропускание сигнала снизу вверх при "попутном" использовании пропускаемого сигнала элементами секции или же передача на выход COUT одного из входных сигналов мультиплексора 4 (переменных BY, G1, G2, констант 0 или 1, конъюнкции G1G2).

LUT-блоки левой пары секций (секций SliceM) способны выполнять две дополнительные функции — блока распределенной памяти и сдвигающего регистра. Блоки распределенной памяти имеют малую емкость (16 бит), могут наращиваться для увеличения емкости, но все же для построения памяти значительных объемов не очень эффективны. Однако они весьма полезны для буферирования данных в любом месте их прохождения.Регистр сдвига может служить разным целям и, в частности, для задержки передаваемых данныхна время от одного до 16 тактов, а при наращивании регистров и до 64 тактов с помощью оборудования одной секции. Программируемые задержки необходимы и для согласования работы ступеней конвейера данных.

Не нашли, что искали? Воспользуйтесь поиском: