ТОР 5 статей:

Методические подходы к анализу финансового состояния предприятия

Проблема периодизации русской литературы ХХ века. Краткая характеристика второй половины ХХ века

Характеристика шлифовальных кругов и ее маркировка

Служебные части речи. Предлог. Союз. Частицы

КАТЕГОРИИ:

- Археология

- Архитектура

- Астрономия

- Аудит

- Биология

- Ботаника

- Бухгалтерский учёт

- Войное дело

- Генетика

- География

- Геология

- Дизайн

- Искусство

- История

- Кино

- Кулинария

- Культура

- Литература

- Математика

- Медицина

- Металлургия

- Мифология

- Музыка

- Психология

- Религия

- Спорт

- Строительство

- Техника

- Транспорт

- Туризм

- Усадьба

- Физика

- Фотография

- Химия

- Экология

- Электричество

- Электроника

- Энергетика

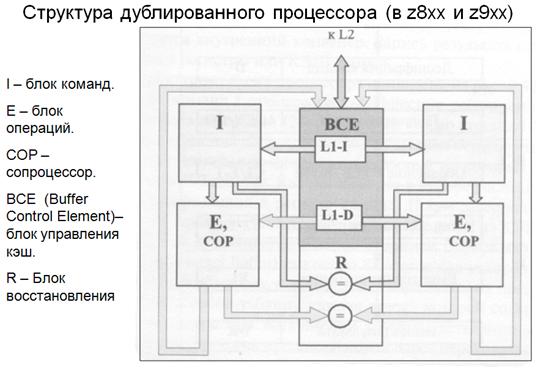

Архитектура IBM zSeries

Современные мэйнфреймы (IBM eServer zSeries) ориентированы на структуру электронного бизнеса. Это предполагает использование серверов различной производительности, специализированного программного обеспечения, высокоскоростных сетей для консолидации ресурсов. Мейнфреймы строятся по принципам организации самонастраивающихся систем:

Автоматическая конфигурация (Self-configuring)

Автоматическое восстановление (Self-healing)

Автоматическая оптимизация (Self-optimizing)

Самозащита (Self-Protecting)

Основные архитектурные особенности современных мэйнфреймов:

-Многопроцесосрная многоузловая конфигурация с включением процессоров различных типов.

-Огромные возможности масштабирования и консолидации.

-Наращивание ресурсов по требованию.

-Способность к логическому разделению ресурсов.

-Средства контроля и восстановления.

-Высокий уровень готовности.

-Минимизация эксплуатационных затрат.

Абсолютный адрес – определяет ячейку памяти (физический).

Реальный адрес – используется для сокращения числа конфликтов, возникающих при обращении процессоров в многопроцессорной системе к наиболее востребованному участку памяти – к векторам прерываний, которые располагаются в начале памяти (0-8196).

Префиксация заключается в изменении адреса, относящегося к 0-8196, на специальный адрес, хранимый в каждом процессоре.

Виртуальный адрес. Используется для виртуализации памяти. Их виду: главный, вторичный, AR-определяемый, базовый.

При преобразовании используется до 5 таблиц, каждая из которых содержит базовый адрес следующей таблицы

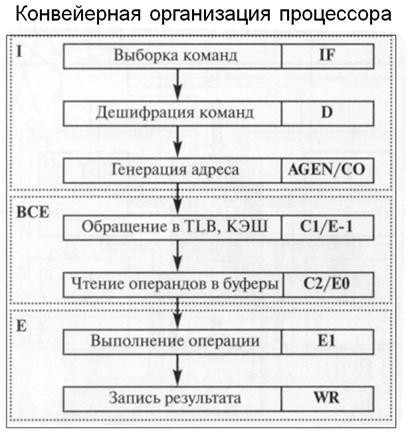

Стараются делать, чтобы стадии срабатывали за 1 такт. КЭШ всегда функционирует по абсолютным адресам. Преобразование виртуального адреса в абсолютный происходит за несколько фаз (C0, C1, C2).

Также используется Absolute Address History Table. На стадии С0 формируется индекс для поиска в AAHT. Если промах в AAHT, то она модифицируется с выполнением всего процесса преобразования по 5 таблицам, который также может быть ускорен с помощью обращения в TLB, где могут храниться части этих пяти таблиц.

Оглавление

1. Принципы построения современных ЭВМ 1

2. Основные тенденции развития ЭВМ 2

3. Архитектуры системы команд 3

4. Типы команд 5

5. Форматы команд. 6

6. Способы адресации 8

7. Обобщенная схема и принцип действия адресного ЗУ. Обобщенная схема и принцип действия ассоциативного ЗУ 10

8. Организация запоминающих массивов адресных ЗУ 12

9. Расслоение памяти 14

10. Статические ЗУ с произвольной выборкой. Запоминающая ячейка 16

11. Микросхема статической памяти 18

12. Диаграмма работы статической памяти 19

13. Динамические ЗУ с произвольной выборкой(DRAM) 20

14. Процесс считывания в динамических ЗУ с произвольной выборкой. Принцип действия усилителя-регенератора. 21

15. Контроллер динамической памяти. 23

16. Микросхема динамической памяти 24

17. Диаграмма работы DRAM памяти. 26

18. Диаграмма работы SDRAM памяти 27

19. Структура ПЗУ (ROM). Классификация ПЗУ. 29

20. Характеристики, влияющие на эффективность кэш-памяти. 30

21. Кэш с произвольной загрузкой, прямым размещением и наборно-ассоциативный кэш. 32

22. Алгоритмы замещения информации в кэш-памяти. Проблема согласования содержимого кэш-памяти и оперативной памяти. 34

23. Страничная организация виртуальной памяти. Сегментная организация виртуальной памяти. Сегментно-страничная организация виртуальной памяти. 35

24. Классификация устройств управления 36

25. Описание автоматов Мура и Мили на языке VHDL 37

26. Описание динамического триггера и дешифратора на языке VHDL 39

27. Описание шифратора и драйвера шины на языке VHDL. 41

28. Описание ОЗУ на языке VHDL 43

29. Управляющие устройства с программируемой логикой (с хранимой в памяти логикой) 44

30. Программируемые логические матрицы. Программируемая матричная логика. Базовые матричные кристаллы. 45

Программируемые логические матрицы и программируемая матричная логика 45

Базовые матричные кристаллы 46

31. Архитектура сложных программируемых логических устройств (CPLD). Структура макроячейки (на примере XC9500). 49

32. Программируемые вентильные матрицы (FPGA). Структура блока типа SLICEL в FPGA Spartan3. 50

33. Процесс проектирования цифровых устройств с использованием ПЛИС. 53

34. Архитектура конвейерного суперскалярного процессора: способы устранения конфликтов по данным. 54

35. Архитектура конвейерного суперскалярного процессора: способы устранения конфликтов по управлению. 56

36. Архитектура конвейерного суперскалярного процессора: статическое и динамическое предсказание переходов. 57

37. Структура процессора P6. 59

38. Процессор P6: регистры замещения. 60

39. Процессор P6: взаимодействие блока шинного интерфейса, кэш-памяти и системной шины. 61

40.Процессор P6: блок вычисления адреса следующей команды. Буфер меток перехода. 62

41. Процессор P6: устройство выборки команд и TLB команд. 63

42. Процессор P6: буфер переупорядоченных команд и буфер команд, готовых к выполнению. 64

43. Процессор P6: буфер переупорядочивания запросов к памяти. Аппаратная и программная предвыборка. 66

44. Отличие архитектуры NetBurst от P6. 67

45. Аппаратные методы ускоренного умножения: умножители по схеме Уоллеса. 68

46. Деление с восстановлением и без восстановления остатка. Структура арифметико-логического устройства для целочисленного деления. 69

47. Организация операций сложения, умножения и деления над числами с плавающей запятой (ЧПЗ). 71

48. Организация шин. Типы шин. Арбитраж шин. 72

49. Шина PCI. Адресация на PCI шине. 74

50. Базовая операция чтения на шине PCI. 75

51. Базовая операция записи на шине PCI. 76

52. Архитектура IBM zSeries 77

Не нашли, что искали? Воспользуйтесь поиском: